# Personal Communications

IC Handbook

# PERSONAL COMMUNICATIONS

IC Handbook

#### Foreword

GEC Plessey Semiconductors are leaders in the growing market of Personal Communications.

The features which identify ICs as being suitable for this market area are *supply current* and *frequency*. Since battery life is all-important in hand-held equipment, every effort is made by our IC designers to develop products which require the absolute minimum current. New ICs such as the SL6639 pager chip and SP8705 (a programmable multi-modulus divider, which consumes only 5mA at 1100MHz) exemplify this philosophy.

New frequency band allocations have been made in the 450 and 900MHz regions for pagers, cordless telephones and cellular radios. GPS bipolar processes have been developed to operate at these and even higher frequencies for dividers, IF amplifiers and single chip synthesisers. The 1 Micron CMOS process is also capable of operating at high frequencies and the latest generation of CMOS synthesisers are included in this handbook.

All the relevant GPS ICs can be supplied in surface mount miniature plastic and some in plastic quad packages in order to satisfy the requirement for small size in compact hand-held radio equipment.

Finally, the Quality Assurance Procedures that are applied to GEC Plessey Semiconductors' products (from consumer electronics to defence projects) are applied to Personal Communications ICs with rigour. Performance and long term reliability are thereby guaranteed in what can be demanding operating environment.

# Contents

|                              | Page |

|------------------------------|------|

| Foreword                     | 2    |

| Product list - by circuit    | 4    |

| Product list - alpha numeric | 6    |

|                              |      |

| Technical Data               | 7    |

|                              |      |

| Maintenance Data             | 185  |

| A 11 12 13 14 1              | 04.4 |

| Application Notes            | 211  |

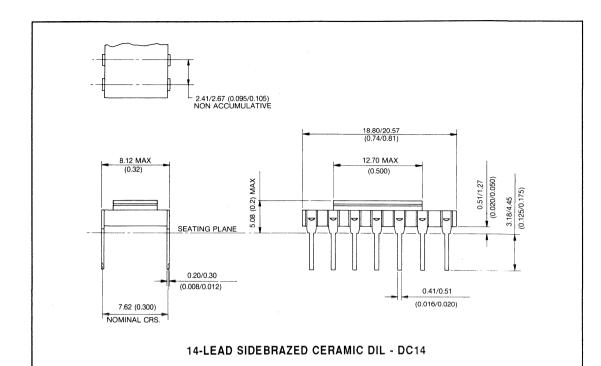

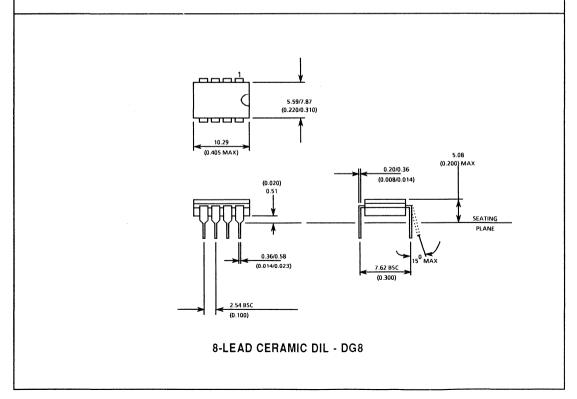

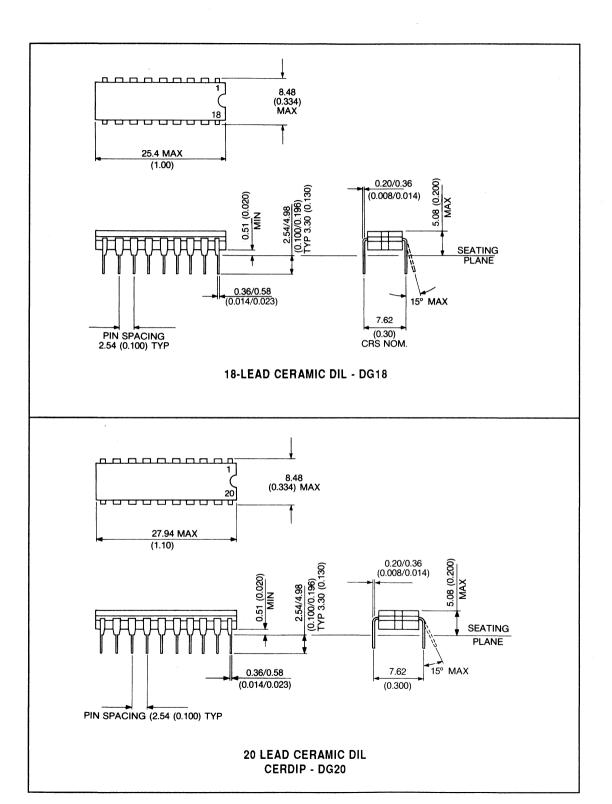

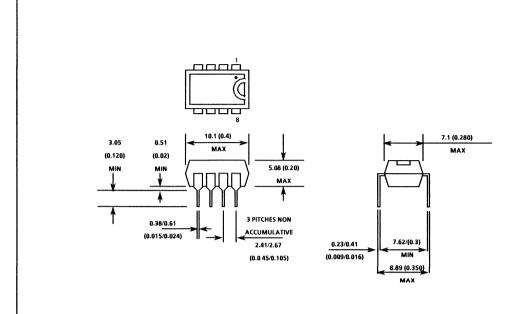

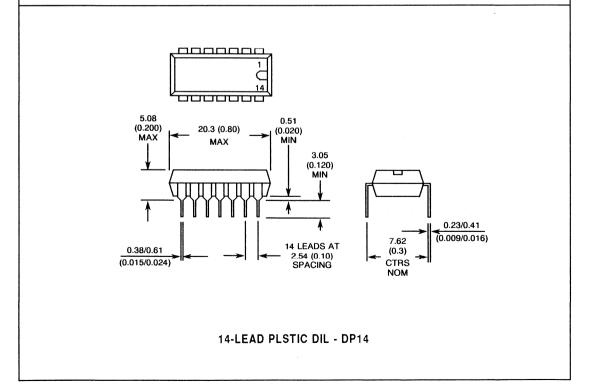

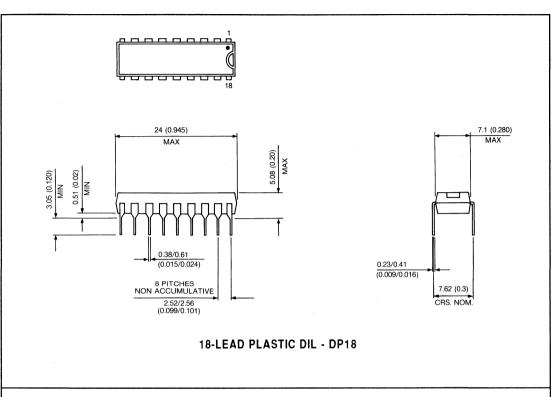

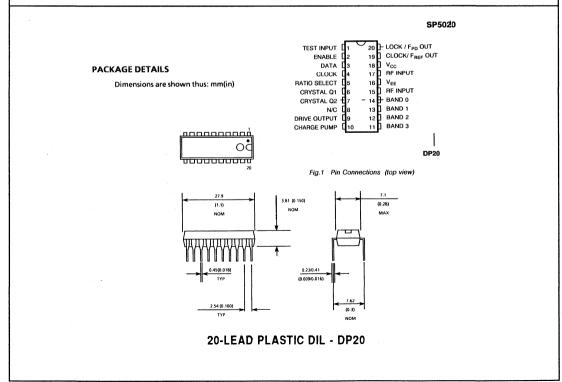

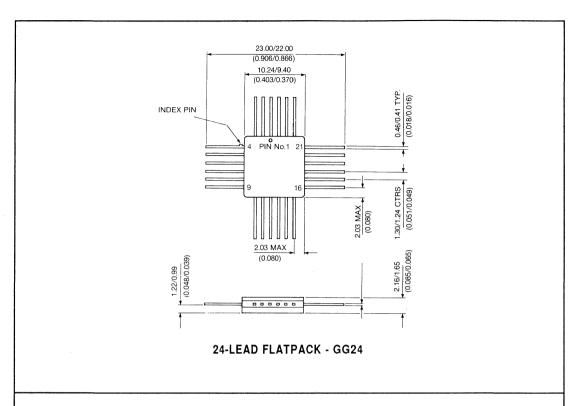

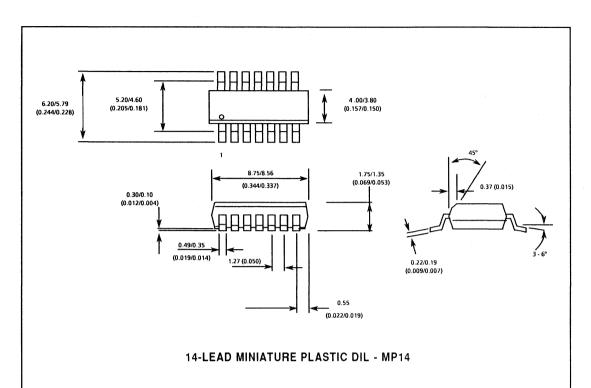

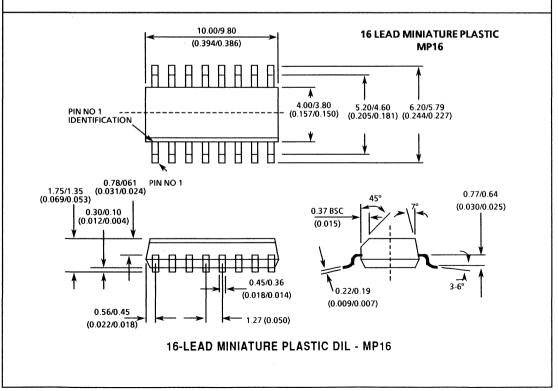

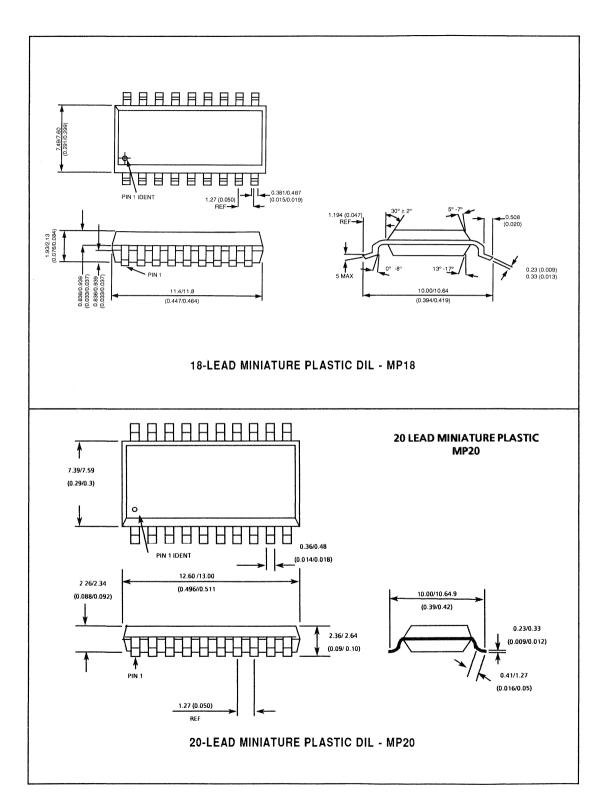

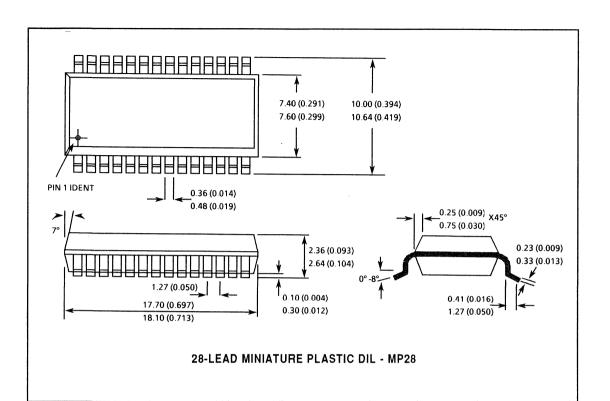

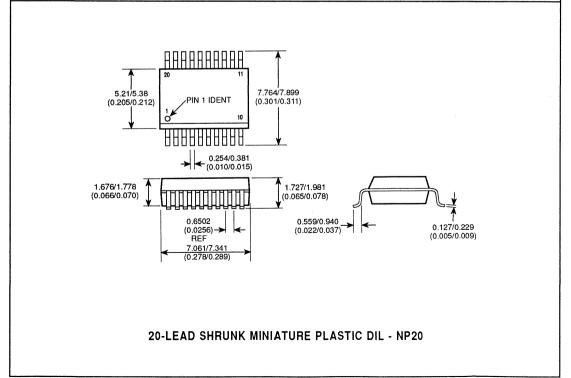

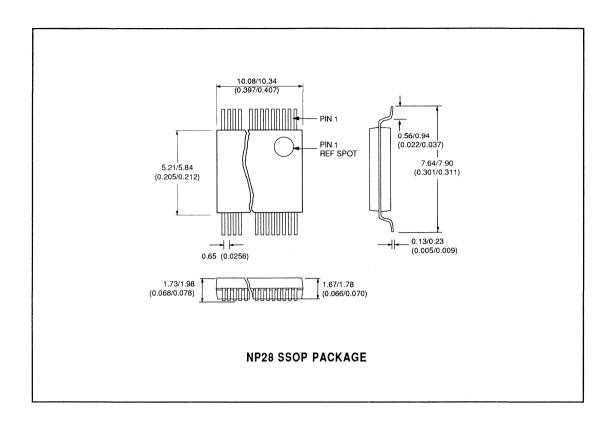

| Package Outlines             | 249  |

| r ackage Outlines            | 240  |

| GPS Locations                | 263  |

# Product List - by circuit type

### PLLs (Phased Lock Loop)

| Type No. | Description                                                                              | Page |

|----------|------------------------------------------------------------------------------------------|------|

| NJ8820   | Frequency synthesiser (PROM interface) (GG** - page 187)                                 | 11   |

| NJ8821   | Frequency synthesiser (microprocessor interface) with resettable counters (GG** - p 193) | 15   |

| NJ88C22  | Frequency synthesiser (microprocessor serial interface)                                  | 20   |

| NJ8823   | Frequency synthesiser (microprocessor interface) with non-resettable counters            | 25   |

| NJ88C24  | Frequency synthesiser (microprocessor serial interface)                                  | 29   |

| NJ88C25  | Frequency synthesiser (microprocessor serial interface)                                  | 34   |

| NJ88C28* | Frequency synthesiser (microprocessor serial interface) with non-resettable counters     | 39   |

| NJ88C30  | VHF synthesiser                                                                          | 46   |

| NJ88C33  | Frequency synthesiser (I2C bus programmable) with current                                | 51   |

| NJ88C41* | Low power frequency synthesiser (3 wire bus)                                             | 61   |

#### **IF Products**

| Type No. | Description                                          | Page |

|----------|------------------------------------------------------|------|

| SL6601C  | FM IF, PLL detector (double conversion) and RF mixer | 110  |

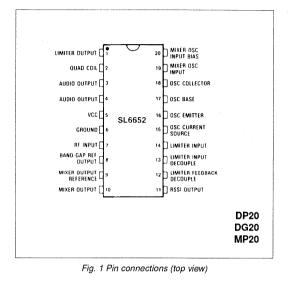

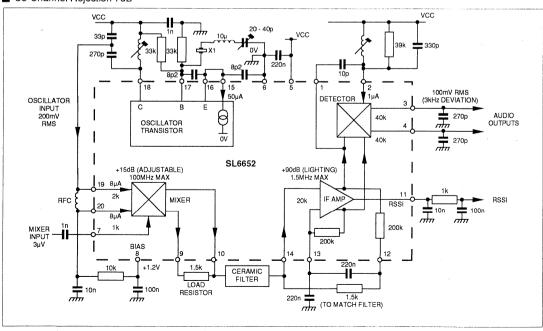

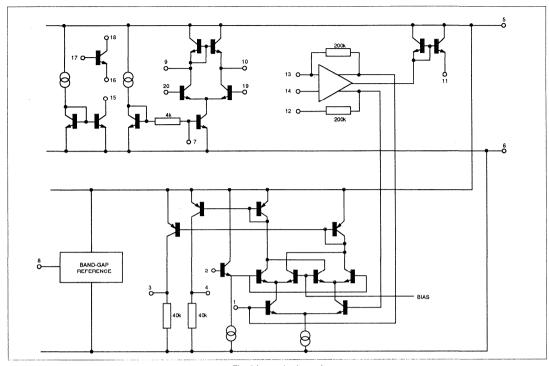

| SL6652   | Low power IF/AF circuit for FM cellular radio        | 127  |

| SL6654   | Low power IF/AF circuit for FM cellular radio        | 134  |

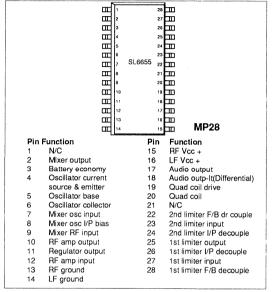

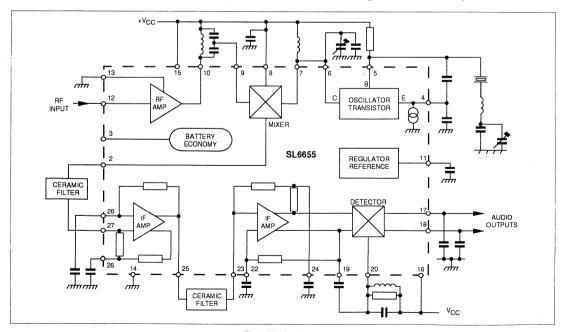

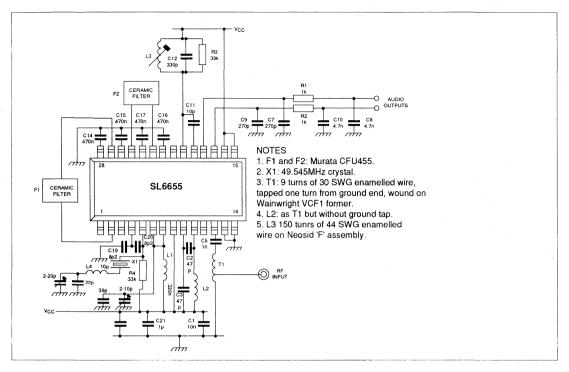

| SL6655   | Superhet receiver                                    | 140  |

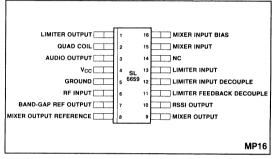

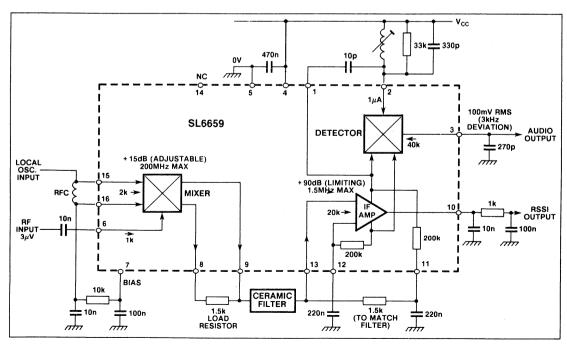

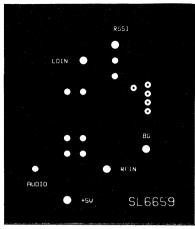

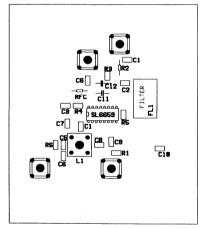

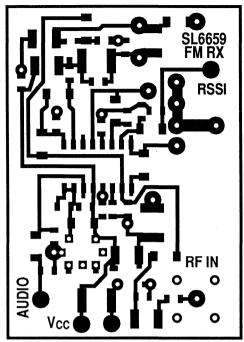

| SL6659   | Low power IF/AF circuit (with RSSI) for FM radio     | 144  |

#### **Prescalers**

| Type No.   | Description                                           | Page |

|------------|-------------------------------------------------------|------|

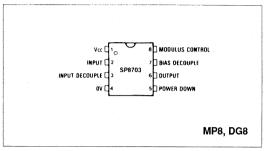

| SP8703     | 1GHz low current divide by 128/129                    | 151  |

| SP8704     | 950MHz very low current divide by 128/129 or 64/64    | 154  |

| SP8705     | 1100MHz very low current divide by 128/129 or 64/64   | 156  |

| SP8706     | 950MHz very low current two-modulus divide by 100/101 | 161  |

| SP8714*    | 2100MHz vey low current multi-modulus divider         | 166  |

| SP8716/8/9 | 520MHz divide by 40/41 + 64/64 + 80/81                | 169  |

| SP8792/3   | 520MHz divide by 80/81 + 40/41                        | 175  |

| SP8795     | 225MHz divide by 32/33                                | 178  |

| SP8799     | 225MHz divide by 10/11                                | 181  |

#### **RF Front Ends**

| Type No. | Description          | Page |

|----------|----------------------|------|

| SL6442   | 1GHz amplifier/mixer | 92   |

| SL6444   | 1GHz amplifier/mixer | 101  |

#### **Amplifiers**

| Type No. | Description                   | Page |

|----------|-------------------------------|------|

| SL560    | 300MHz low noise amplifier    | 62   |

| SL562    | Low noise programmable op-amp | 67   |

| SL1610   | RF/IF Amplifier               | 70   |

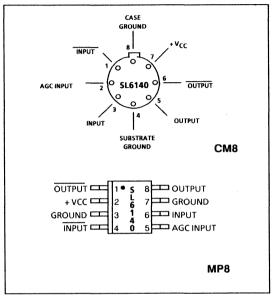

| SL6140   | 400MHz wideband AGC amplifier | 78   |

| SL6270C  | Gain controlled pre-amplifier | 86   |

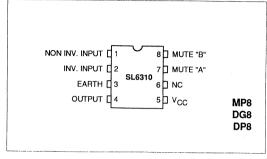

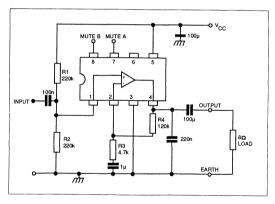

| SL6310C  | Switchable audio amplifier    | 89   |

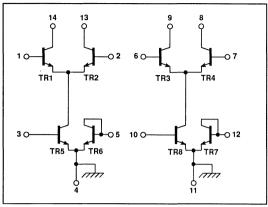

#### **Transistor Arrays**

| Type No.   | Description                            | Page |

|------------|----------------------------------------|------|

| SL2363C/4C | Very high performance transistor array | 73   |

| SL2365     | Very high performance transistor array | 75   |

| SL2366     | High performance transistor array      | 76   |

#### **CODEC**

| Type No. | Description                                                  | Page |

|----------|--------------------------------------------------------------|------|

| MV3100*  | 3V CODEC with analog interface for digital mobile telephones | 9    |

#### Paging Receivers & Decoders

| Type No.   | Description                                | Page |

|------------|--------------------------------------------|------|

| MV6639*    | POCSAG decoder                             | 10   |

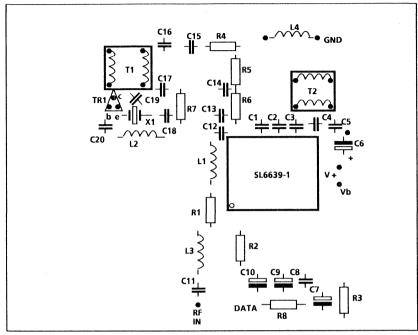

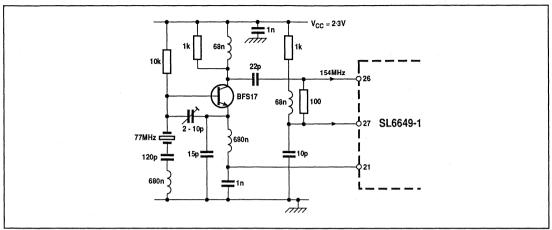

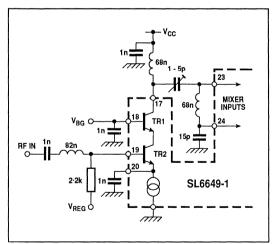

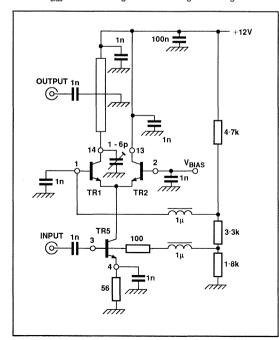

| SL6639-1** | 200MHz direct conversion FSK data receiver | 198  |

| SL6649-1   | 200MHz direct conversion FSK data receiver | 116  |

<sup>\*</sup> Outline or development details only - contact GPS Customer Services (see page 263)

<sup>\*</sup> For maintenance purposes only

# Product List - alpha numeric

| Type No.   | Description                                                                                 | Page       |

|------------|---------------------------------------------------------------------------------------------|------------|

| MV3100*    | 3V CODEC with analog interface for digital mobile telephones                                | 9          |

| MV6639*    | POCSAG decoder                                                                              | 10         |

| NJ8820     | Frequency synthesiser (PROM interface) (GG** - page 187)                                    | 11         |

| NJ8821     | Frequency synthesiser (microprocessor interface) with resettable counters (GG** - page 193) | 16         |

| NJ88C22    | Frequency synthesiser (microprocessor serial interface)                                     | 20         |

| NJ8823     | Frequency synthesiser (microprocessor interface) with non-resettable counters               | 25         |

| NJ88C24    | Frequency synthesiser (microprocessor serial interface)                                     | 29         |

| NJ88C25    | Frequency synthesiser (microprocessor serial interface)                                     | 34         |

| NJ88C28*   | Frequency synthesiser (microprocessor serial interface) with non-resettable counters        | 39         |

| NJ88C30    | VHF synthesiser                                                                             | 46         |

| NJ88C33    | Frequency synthesiser (I2C bus programmable) with current source phase detector outputs     | 51         |

| NJ88C41*   | Low power frequency synthesiser (3 wire bus)                                                | 61         |

| SL560      | 300MHz low noise amplifier                                                                  | 62         |

| SL562      | Low noise programmable op-amp                                                               | 67         |

| SL1610     | RF/IF Amplifier                                                                             | 70         |

| SL2363C    | Very high performance transistor array                                                      | 73         |

| SL2364C    | Very high performance transistor array                                                      | 73         |

| SL2365     | Very high performance transistor array                                                      | 75         |

| SL2366     | High performance transistor array                                                           | 76         |

| SL6140     | 400MHz wideband AGC amplifier                                                               | 78         |

| SL6270C    | Gain controlled pre-amplifier                                                               | 86         |

| SL6310C    | Switchable audio amplifier                                                                  | 89         |

| SL6442     | 1GHz amplifier/mixer                                                                        | 92         |

| SL6444     | 1GHz amplifier/mixer                                                                        | 101        |

| SL6601C    | FM IF, PLL detector (double conversion) and RF mixer                                        | 110        |

| SL6639-1** | 200MHz direct conversion FSK data receiver                                                  | 198        |

| SL6649-1   | 200MHz direct conversion FSK data receiver                                                  | 116        |

| SL6652     | Low power IF/AF circuit for FM cellular radio                                               | 127        |

| SL6654     | Low power IF/AF circuit for FM cellular radio                                               | 134        |

| SL6655     | Superhet receiver                                                                           | 140        |

| SL6659     | Low power IF/AF circuit (with RSSI) for FM radio                                            | 144        |

| SP8703     | 1GHz low current divide by 128/129                                                          | 151        |

| SP8704     | 950MHz very low current divide by 128/129 or 64/64                                          | 154        |

| SP8705     | 1100MHz very low current divide by 128/129 or 64/64                                         | 156        |

| SP8706     | 950MHz very low current two-modulus divide by 100/101                                       | 161        |

| SP8714*    | 2100MHz very low current multi-modulus divider                                              | 166        |

| SP8716     | 520MHz divide by 40/41                                                                      | 169        |

| SP8718     | 520MHz divide by 64/64                                                                      | 169<br>169 |

| SP8719     | 520MHz divide by 80/81                                                                      | 172        |

| SP8789     | 225MHz divide by 20/21                                                                      | 175        |

| SP8792     | 225MHz divide by 80/81                                                                      | 175        |

| SP8793     | 225MHz divide by 40/41                                                                      | 178        |

| SP8795     | 225MHz divide by 32/33                                                                      | 181        |

| SP8799     | 225MHz divide by 10/11                                                                      | 101        |

<sup>\*</sup> Outline or development details only - contact GPS Customer Services (see page 263)

<sup>\*\*</sup> For maintenance purposes only

# Technical Data

# MV3100

# 3V CODEC WITH ANALOG INTERFACE FOR DIGITAL MOBILE TELEPHONES

The MV3100 is a complete integrated audio interface for digital mobile telephones. Using mixed signal CMOS technology the device contains a DSP CODEC for audio to PCM conversion, together with gain programmable microphone and loudspeaker amplifiers. The use of DSP architecture for the CODEC function enables device operation from supplies of 2.7V upwards and allows software programmability of gain characteristics. The device requires a minimum of external components giving a physically small solution, ideal for hand-portable telephones.

#### **FEATURES**

- Highly integrated solution with on-chip audio interface

- Low voltage operation, 2.7V to 5.5V

- Low power consumption, 32mW typ.

- Excellent RF immunity

- 16Bit linear PCM interface

- Gain programmability supports many microphone and loudspeaker types

- On-chip PLL generates all internal clocks

- Programmable sidetone

#### **APPLICATIONS**

- Digital Cordless Telephones (CT2, DECT, JDCT, Spread Spectrum)

- Digital Cellular Telephones (GSM, ADC, JDC)

- Digital Mobile Radio

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage

-0.3V to +7V

Input Voltage

-0.3V to Vpp +0.3V

Operating Temperature

-30°C to +70°C

Storage Temperature

-55°C to +125°C

# MV6639

#### POCSAG DECODER

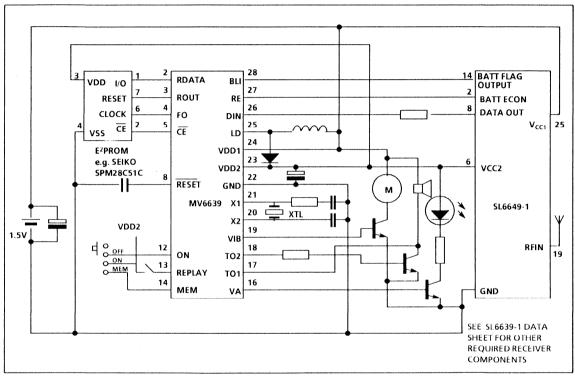

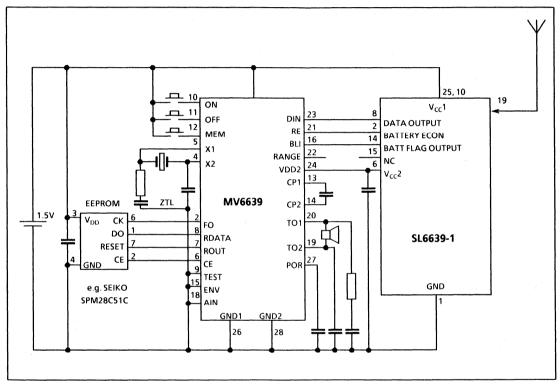

The MV6639 POCSAG decoder is capable of operating at 512 or 1200 baud. This device together with a suitable receiver provide the major components for a POCSAG pager.

POCSAG is the acronym for Post Office Code Standardisation Advisory Group. The POCSAG code is the most accepted radio paging standard, (CCIR RPC No.1) and provides for over 2 million pager ID's, two of which may be held in this device. The POCSAG code format is shown in figure 3.

The design is optimised for very low power, low voltage use. Advanced features allow the decoder to be used in a wide range of applications.

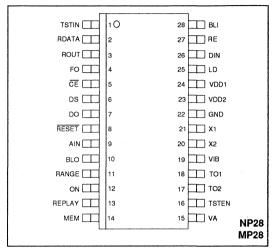

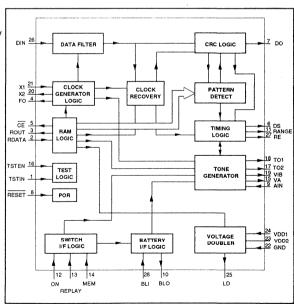

The pinout and architecture are shown in figures 1 and 2

#### **FEATURES**

- Tone only and/or messaging pager at 512 or 1200 baud using a single 32768Hz crystal

- Low voltage supply (1 V min.)

- Low current consumption (100µA max.)

- Interface to SL6649- 1 radio receiver chip

- True 2 bit CRC error correction

- Voltage doubler for radio receiver or µP and Display

- Programmable tone generator output frequency (2048 or 2731 Hz)

#### **APPLICATIONS**

- Wrist watch pager

- Message display pager

- Tone only pager

- Data receivers

#### ABSOLUTE MAXIMUM RATINGS

Supply voltage (VDD1 - GND)

-0.5V to 5V

Voltage on any pin

-0.3V to VDD1 + 0.3V

Operating temperature Storage temperature

-20°C to + 70°C

-55°C to +125°C

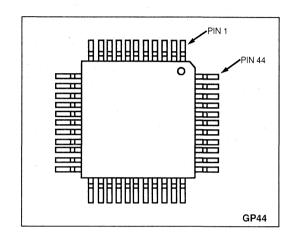

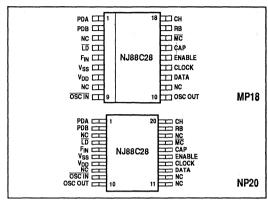

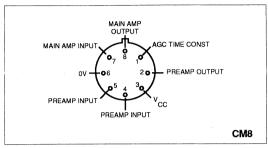

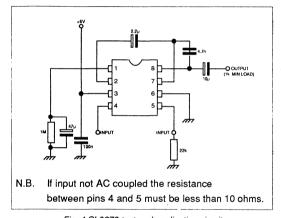

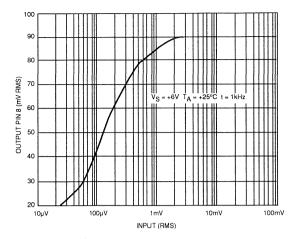

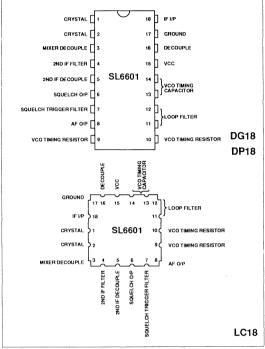

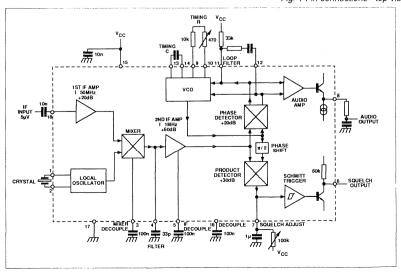

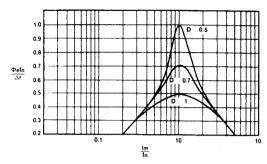

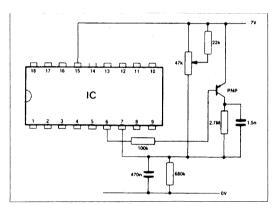

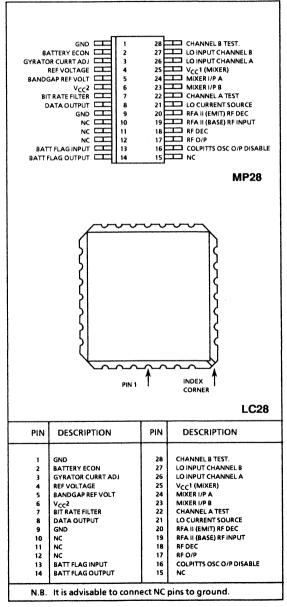

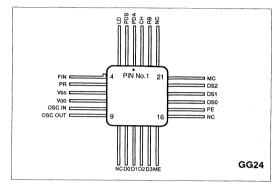

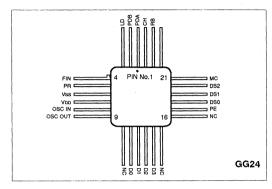

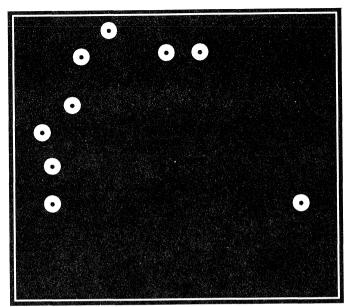

Fig. 1 Pin connection (top view - not to scale)

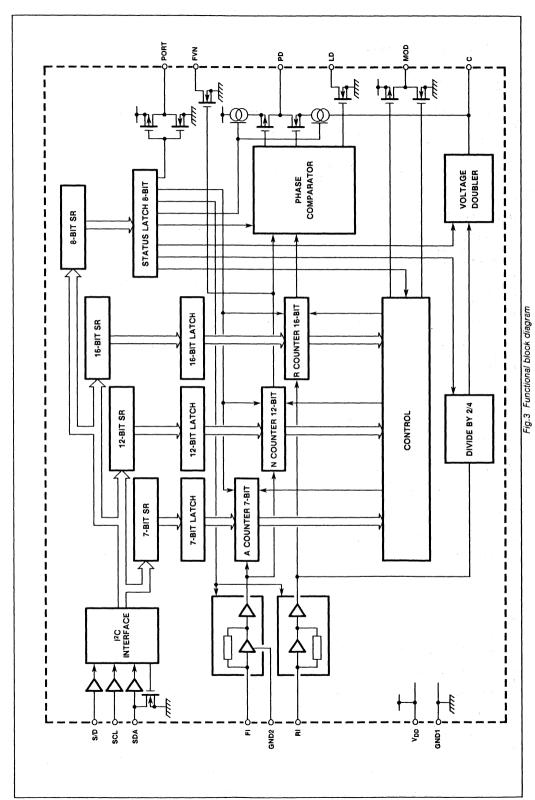

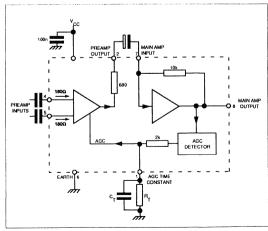

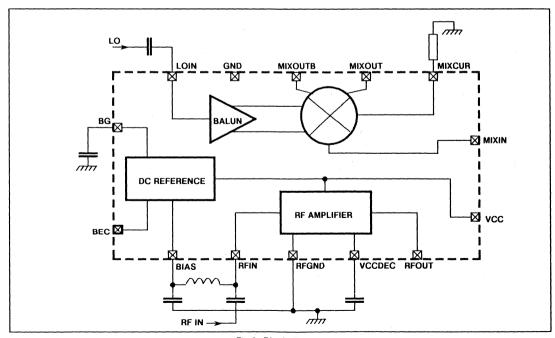

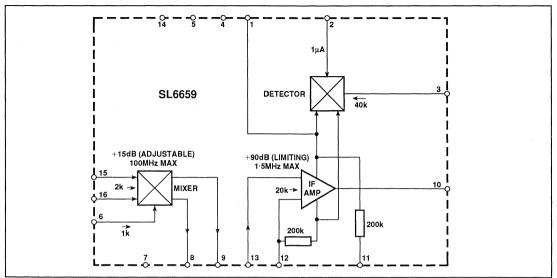

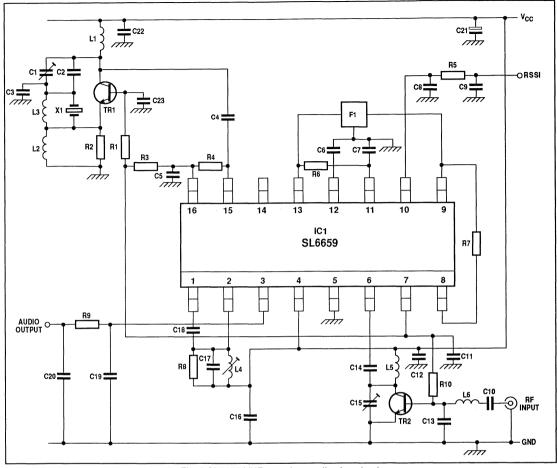

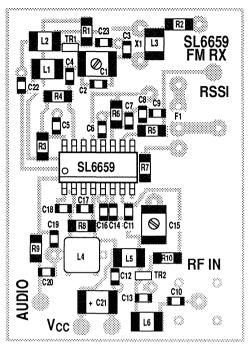

Fig. 2 MV6639 Block Diagram

# NJ8820

#### FREQUENCY SYNTHESISER (PROM INTERFACE)

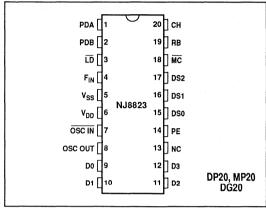

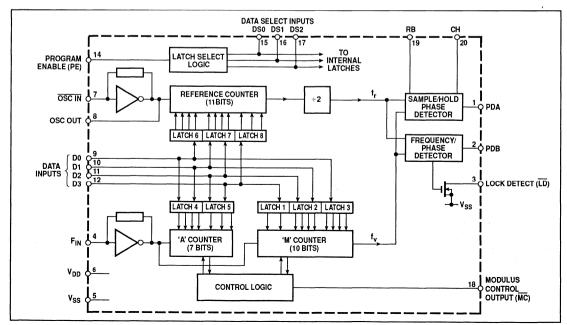

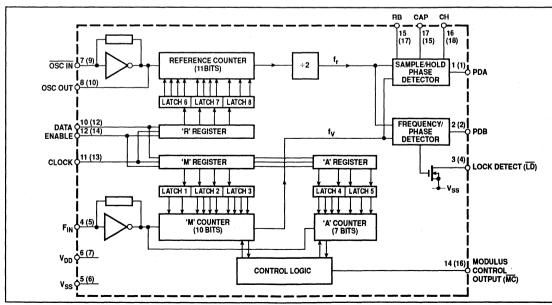

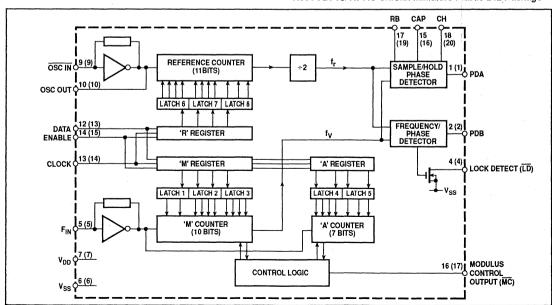

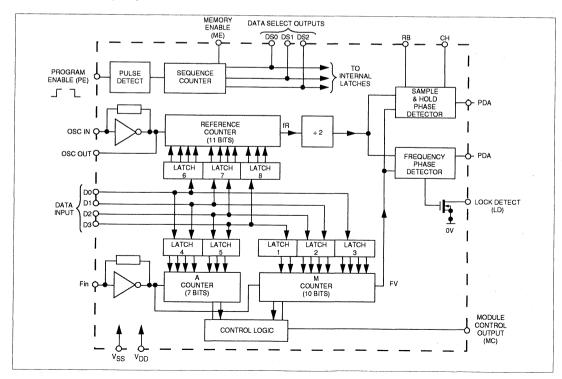

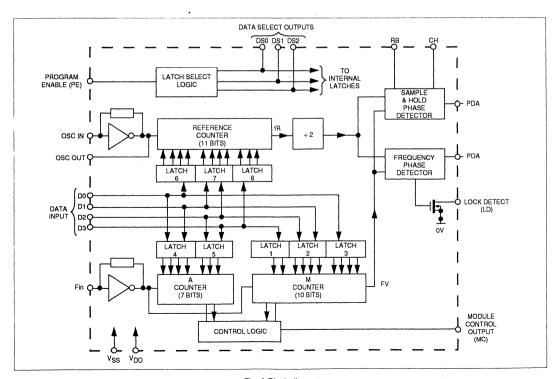

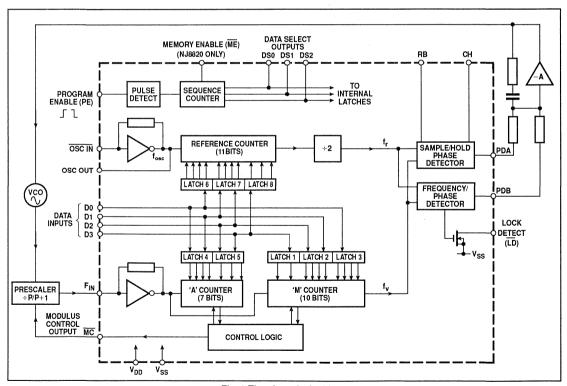

The NJ8820 is a synthesiser circuit fabricated on the GPS CMOS process and is capable of achieving high sideband attenuation and low noise performance. It contains a reference oscillator, 11-bit programmable reference divider, digital and sample-and-hold comparators, 10-bit programmable 'M' counter, 7-bit programmable 'A' counter and the necessary control and latch circuitry for accepting and latching the input data.

Data is presented as eight 4-bit words read from an external memory, with the necessary timing signals generated internally.

It is intended to be used in conjunction with a two-modulus

It is intended to be used in conjunction with a two-modulus prescaler such as the SP8710 series to produce a universal binary coded synthesiser.

The NJ8820 is available in Plastic DIL (DP) and Miniature Plastic DIL (MP) packages, both with operating temperature range of  $-30^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$ . The NJ8820MA is available only in Ceramic DIL package with operating temperature range of  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ .

#### **FEATURES**

- Low Power Consumption

- Direct Interface to ROM or PROM

- High Performance Sample and Hold Phase Detector

- >10MHz Input Frequency

#### ORDERING INFORMATION

NJ8820 BA DP Plastic DIL Package

NJ8820 BA MP Miniature Plastic DIL Package

NJ8820 MA DG Ceramic DIL Package

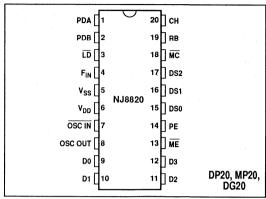

Fig. 1 Pin connections - top view

#### **ABSOLUTE MAXIMUM RATINGS**

Supply voltage,  $V_{DD}-V_{SS}$  -0.5V to 7V Input voltage Open drain outputs, pins 3 and 13 7V All other pins  $V_{SS}-0.3V$  to  $V_{DD}+0.3V$  Storage temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$  (DG package, NJ8820MA) Storage temperature  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

-55°C to +125°C (DP and MP packages, NJ8820)

DATA SELECT MEMORY ENABLE OUTPUTS СН (ME) DS0 DS1 DS2 RB 13 15 16 19 20 TO INTERNAL PULSE SEQUENCE PROGRAM DETECT COUNTER ENABLE (PE) Г٦ REFERENCE COUNTER OSC IN SAMPLE/HOLD (11BITS) PHASE PDA DETECTOR OSC OUT LATCH 6 LATCH 7 LATCH 8 FREQUENCY PHASE DETECTOR D0 D1 D2 LOCK DETECT (LD) D3 ٧ss LATCH 4 LATCH 5 LATCH 1 LATCH 2 LATCH 3 'A' COUNTER 'M' COUNTER (7 BITS) (10 BITS) MODULUS CONTROL LOGIC CONTROL OUTPUT (MC)

Fig.2 Block diagram

#### ELECTRICAL CHARACTERISTICS AT VDD = 5V

Test conditions unless otherwise stated:

$V_{DD}-V_{SS}=5V\pm0.5V$ . Temperature range NJ8820 BA:  $-30^{\circ}$ C to  $+70^{\circ}$ C; NJ8820 MA:  $-40^{\circ}$ C to  $+85^{\circ}$ C DC Characteristics

| Characteristic                | Value                       |            | Units      | 0 !!!!   |                                                            |

|-------------------------------|-----------------------------|------------|------------|----------|------------------------------------------------------------|

| Ondradicition                 |                             | Тур.       | Max.       | Oilles   | Conditions                                                 |

| Supply current                |                             | 3·5<br>0·7 | 5·5<br>1·5 | mA<br>mA | $f_{OSC}$ , $f_{FIN} = 10MHz$ 0 to 5V                      |

| OUTPUT LEVELS                 |                             | 0.7        | 13         | l IIIA   | f <sub>osc</sub> , f <sub>FIN</sub> = 1·0MHz∫ square wave  |

| Memory Enable Output (ME)     |                             |            |            |          |                                                            |

| Low level                     |                             |            | 0.4        | V        | I <sub>SINK</sub> = 4mA                                    |

| Open drain pull-up voltage    |                             |            | 7          | l v      | SIIV                                                       |

| Data Select Outputs (DS0-DS2) |                             |            |            |          |                                                            |

| High level                    | 4.6                         |            |            | V        | I <sub>SOURCE</sub> = 1mA                                  |

| Low level                     |                             |            | 0.4        | V        | I <sub>SINK</sub> = 2mA                                    |

| Modulus Control Output (MC)   |                             |            |            |          | SHAK                                                       |

| High level                    | 4.6                         |            |            | V        | I <sub>SOURCE</sub> = 1mA                                  |

| Low level                     |                             |            | 0.4        | V        | I <sub>SINK</sub> = 1mA                                    |

| Lock Detect Output (LD)       | <u> </u>                    |            |            |          |                                                            |

| Low level                     |                             |            | 0.4        | V        | I <sub>SINK</sub> = 4mA                                    |

| Open drain pull-up voltage    |                             |            | 7          | V        |                                                            |

| PDB Output                    |                             |            |            |          | ·                                                          |

| High level                    | 4.6                         |            |            | V        | I <sub>SOURCE</sub> = 5mA                                  |

| Low level                     |                             |            | 0.4        | V        | I <sub>SINK</sub> = 5mA                                    |

| 3-state leakage current       |                             |            | ±0·1       | μΑ       |                                                            |

| INPUT LEVELS                  |                             |            |            |          |                                                            |

| Data Inputs (D0-D3)           |                             |            |            |          |                                                            |

| High level                    | 4.25                        |            |            | V        | TTL compatible                                             |

| Low level                     | 1                           |            | 0.75       | V        | See note 1                                                 |

| Program Enable Input (PE)     |                             |            |            |          |                                                            |

| Trigger level                 | V <sub>BIAS</sub><br>±100mV |            |            | V        | $V_{BIAS}$ = self-bias point of PE (nominally $V_{DD}/2$ ) |

#### **AC Characteristics**

| Characteristic                                                  |      | Value     |    | Units |                                                     |  |

|-----------------------------------------------------------------|------|-----------|----|-------|-----------------------------------------------------|--|

| Characteristic                                                  | Min. | Min. Typ. |    | Units | Conditions                                          |  |

| F <sub>IN</sub> and OSC IN input level                          | 200  |           |    | mVRMS | 10MHz AC-coupled sinewave                           |  |

| Max. operating frequency, f <sub>FIN</sub> and f <sub>osc</sub> | 10.6 |           |    | MHz   | Input squarewave $V_{DD}$ to $V_{SS}$ , See note 5. |  |

| Propagation delay, clock to MC                                  |      | 30        | 50 | ns    | See note 2.                                         |  |

| PE pulse length, tw                                             | 5    |           |    | μs    | Pulse to V <sub>SS</sub> or V <sub>DD</sub> .       |  |

| Data set-up time, t <sub>DS</sub>                               | 1    |           |    | μs    |                                                     |  |

| Data hold time, t <sub>DH</sub>                                 | 10   |           |    | ns    |                                                     |  |

| Digital phase detector propagation delay                        |      | 500       |    | ns    | •                                                   |  |

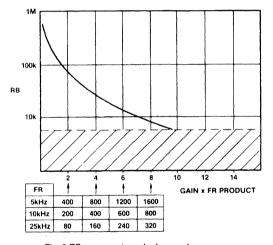

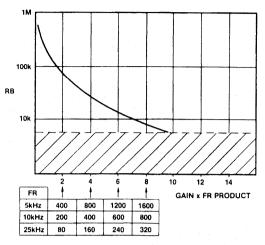

| Gain programming resistor, RB                                   | 5    |           |    | kΩ    |                                                     |  |

| Hold capacitor, CH                                              |      |           | 1  | nF    | See note 3.                                         |  |

| Output resistance, PDA                                          | . [  |           | 5  | kΩ    |                                                     |  |

| Digital phase detector gain                                     |      | 0.4       |    | V/Rad |                                                     |  |

| Power supply rise time                                          | 100  |           |    | μs    | 10% to 90%, see note 4.                             |  |

|                                                                 | 1    | 1         | l  | i i   |                                                     |  |

- 1. Data inputs have internal pull-up resistors to enable them to be driven from TTL outputs.

- 2. All counters have outputs directly synchronous with their respective clock rising edges.

- 3. The finite output resistance of the internal voltage follower and 'on' resistance of the sample switch driving this pin will add a finite time constant to the loop. An external 1nF hold capacitor will give a maximum time constant of 5µs, typically.

4. To ensure correct operation of power-on programming.

- 5. Operation at up to 15MHz is possible with a full logic swing but is not guaranteed.

#### PIN DESCRIPTIONS

| Pin no.      | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 .          | PDA                | Analog output from the sample and hold phase comparator for use as a 'fine' error signal. Output at $(V_{DD}-V_{SS})/2$ when the system is in lock. Voltage increases as $f_{r}$ phase lead increases; voltage decreases as $f_{r}$ phase lead increases. Output is linear over only a narrow phase window, determined by gain (programmed by RB).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2            | PDB                | Three-state output from the phase/frequency detector for use as a 'coarse' error signal. $f_V > f_\Gamma \text{ or } f_V \text{ leading: positive pulses with respect to the bias point } V_{BIAS} \\ f_V < f_\Gamma \text{ or } f_\Gamma \text{ leading: negative pulses with respect to the bias point } V_{BIAS} \\ f_V = f_\Gamma \text{ and phase error within PDA window: high impedance.}$                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3            | LD                 | An open-drain lock detect output at low level when phase error is within PDA window (in lock); high impedance at all other times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4            | F <sub>IN</sub>    | The input to the main counters, normally driven from a prescaler, which may be AC-coupled or, when a full logic swing is available, may be DC-coupled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5            | $V_{SS}$           | Negative supply (ground).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6            | $V_{DD}$           | Positive supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7, 8         | OSC IN/<br>OSC OUT | These pins form an on-chip reference oscillator when a series resonant crystal is connected across them. Capacitors of appropriate value are also required between each end of the crystal and ground to provide the necessary additional phase shift. An external reference signal may, alternatively, be applied to $\overline{OSC\ IN}$ . This may be a low-level signal, AC-coupled, or if a full logic swing is available it may be DC-coupled. The program range of the reference counter is 3 to 2047, with the division ratio being twice the programmed number.                                                                                                                                                                                                                                                           |

| 9,10, 11, 12 | D0-D3              | Information on these inputs is transferred to the internal data latches during the appropriate data read time slot. D3 is MSB, D0 is LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13           | ME                 | An open drain output for use in controlling the power supply to an external ROM or PROM. ME is low during the data read period and high impedance at other times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14           | PE                 | A positive or negative pulse or edge AC-coupled into this pin initiates the single-shot data read procedure. Grounding this pin repeats the data read procedure in a cyclic manner.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15, 16, 17   | DS0-DS2            | Internally generated three-state data select outputs, which may be used to address external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18           | MC                 | Modulus control output for controlling an external dual-modulus prescaler. $\overline{\text{MC}}$ will be low at the beginning of a count cycle and will remain low until the 'A' counter completes its cycle. $\overline{\text{MC}}$ then goes high and remains high until the 'M' counter completes its cycle, at which point both 'A' and 'M' counters are reset. This gives a total division ratio of $MP+A$ , where $P$ and $P+1$ represent the dual-modulus prescaler values. The program range of the 'A' counter is 0-127 and therefore can control prescalers with a division ratio up to and including $\div$ 128/129. The programming range of the 'M' counter is 8-1023 and, for correct operation, $M \!\! > \!\! A$ . Where every possible channel is required, the minimum total division ratio should be $P^2-P$ . |

| 19           | RB                 | An external sample and hold phase comparator gain programming resistor should be connected between this pin and $V_{\rm SS}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20           | СН                 | An external hold capacitor should be connected between this pin and $V_{SS}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

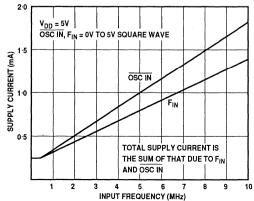

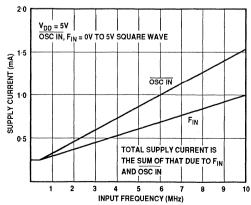

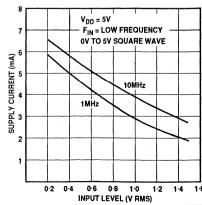

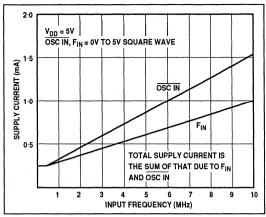

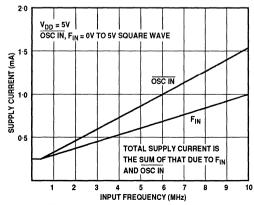

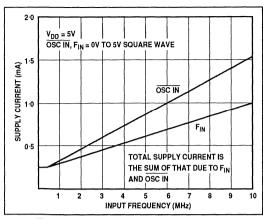

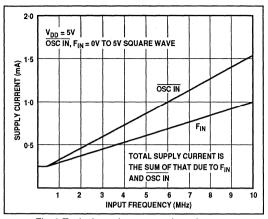

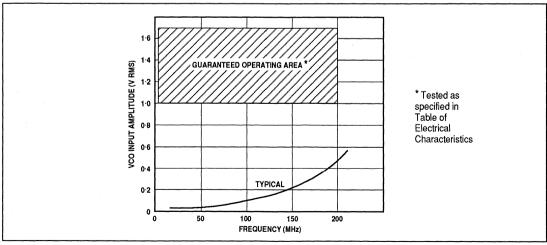

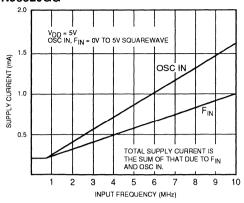

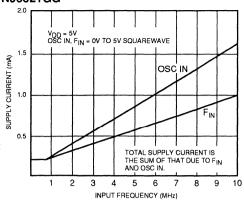

Fig. 3 Typical supply current v. input frequency

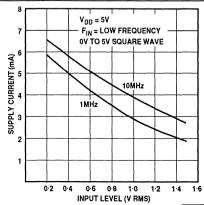

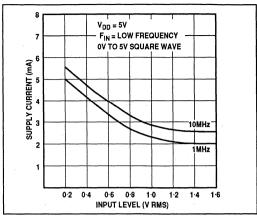

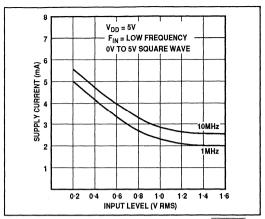

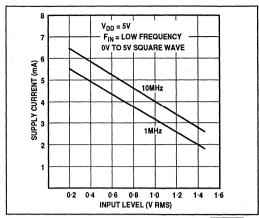

Fig. 4 Typical supply current v. input level, OSC IN

#### **PROGRAMMING**

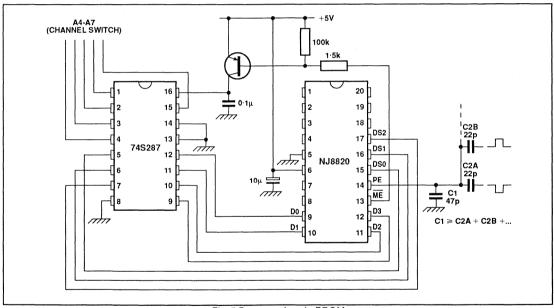

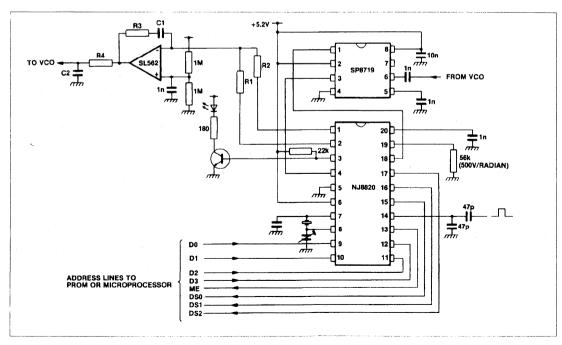

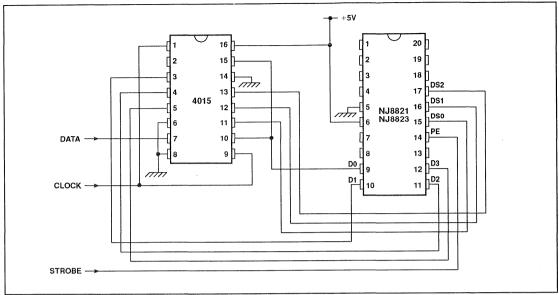

Program information can be obtained from an external ROM or PROM under the control of the NJ8820. Twenty-eight data bits are required per channel arranged as eight 4-bit words leaving four redundant bits, two of which are available on the data bus driving the data transfer time slot and may be used for external control purposes. A suitable PROM would be the 74S287, giving up to 32 channel capability as shown in Fig. 5. Note that the choice of PNP transistor and supply bypass capacitor on the ROM should be such that the ROM will power up in time: for example, at 10MHz oscillator frequency, the ROM must be powered up in less than 25us.

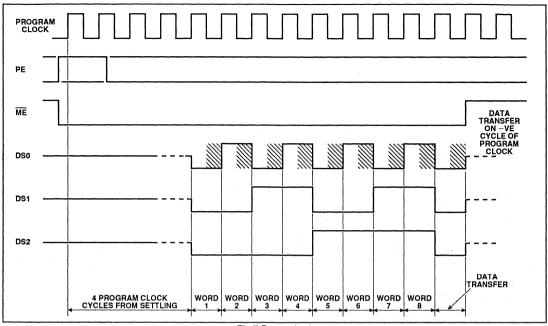

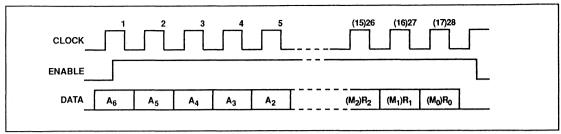

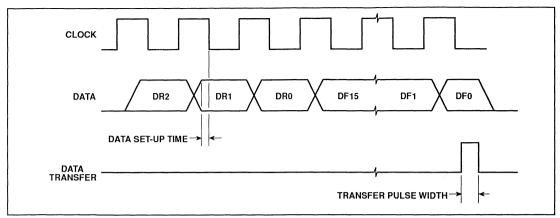

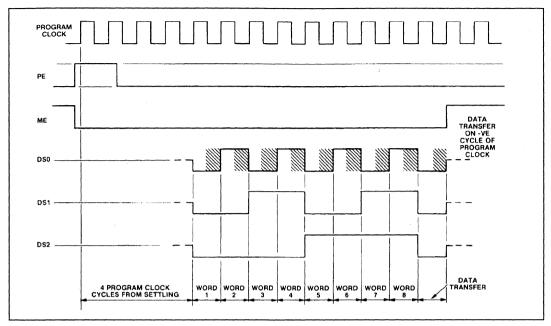

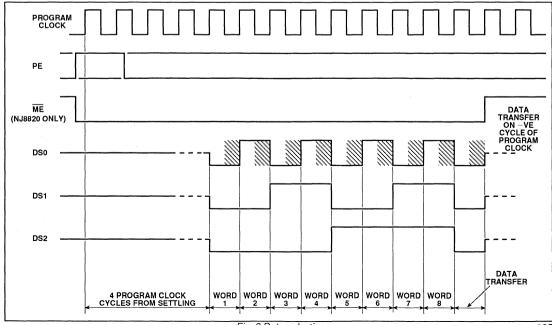

Reading this data is normally done in single shot mode, with the data read cycle started by either a positive or negative pulse on the program enable (PE) pin. The data read cycle is generated from a program clock at 1/64 of the reference oscillator frequency. A memory enable signal (ME) is supplied to allow power-down of the ROM when it is not in use. Data select outputs (DS0-DS2) remain in a high impedance state when the program cycle is completed to allow the address bus to be used for other functions if desired. The data map, data read cycle and timing diagram are shown in Figs. 6 as. Data is latched internally during the portions of the program cycle shown shaded in Fig. 7 and all data is transferred to the

counters and latched during the data transfer time slot.

Alternatively, the PE pin may be grounded, causing the data read cycle to repeat cyclically to allow continuous up-dating of the program information. In this mode, external memory will be enabled continuously ( $\overline{\text{ME}}$  low) and the data read cycle will repeat every sixteen cycles of the internal program clock, i.e. every  $1024/f_{\text{OSC}}$  seconds. This programming method is not recommended because the higher power consumption and the possibilities of noise into the loop from the digital data lines.

#### **Power-on Programming**

On power-up, the data read cycle is automatically initiated, making it unnecessary to provide a PE pulse. The circuit detects the power supply rising above a threshold point (nominally 1-5V) and, after an internally generated delay to allow the supply to rise fully, the circuit is programmed in the normal way. This delay is generated by counting reference oscillator pulses and is therefore dependent on the crystal used. The delay consists of 53248 reference oscillator cycles, giving a delay of about 5ms at 10MHz.

To ensure correct operation of this function, the power supply rise time should be less than 5ms (at 10MHz), rising smoothly through the threshold point.

Fig. 5 Programming via PROM

| WORD                                 | DS2                             | DS1                        | DS0                        | D3                                    | D2                                            | D1                                     | D0                                     |

|--------------------------------------|---------------------------------|----------------------------|----------------------------|---------------------------------------|-----------------------------------------------|----------------------------------------|----------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1 | M1<br>M5<br>M9<br>A3<br>-<br>R3<br>R7 | M0<br>M4<br>M8<br>A2<br>A6<br>R2<br>R6<br>R10 | M3<br>M7<br>A1<br>A5<br>R1<br>R5<br>R9 | M2<br>M6<br>A0<br>A4<br>R0<br>R4<br>R8 |

Fig. 6 Data map

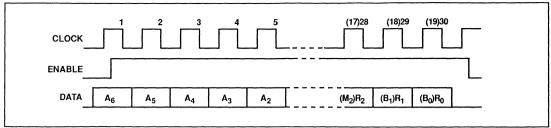

Fig.7 Data selection

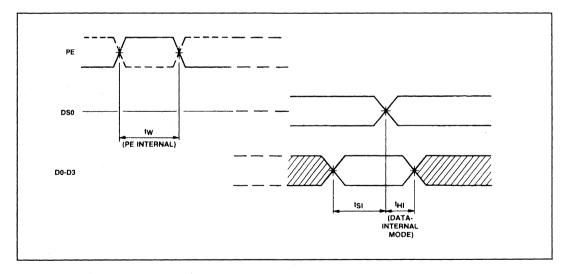

Fig.8 Timing diagram

#### PHASE COMPARATORS

The digital phase/frequency detector drives a three-state output, PDB, which provides a 'coarse' error signal to enable fast switching between channels. The PDB output is active until the phase error is within the sample and hold phase detector, PDA, window, when PDB becomes high impedance. Phase-lock is indicated at this point by a low level on  $\overline{\text{LD}}$ . The sample and hold phase detector provides a 'fine' error signal to give further phase adjustment and to hold the loop in lock.

An internally generated ramp, controlled by the digital output from both the reference and main divider chains, is sampled at the reference frequency to give the 'fine' error signal, PDA. When in phase lock, this output would be typically at (V<sub>DD</sub>-V<sub>SS</sub>)/2 and any offset from this would be proportional to phase error. The relationship between this offset and the

phase error is the phase comparator gain, which is programmable with an external resistor, RB. An internal 50pF capacitor is used in the sample and hold comparator.

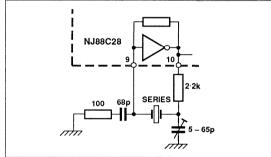

#### **CRYSTAL OSCILLATOR**

When using the internal oscillator, the stability may be enhanced at high frequencies by the inclusion of a resistor between pin 8 (OSC OUT) and the other components. A value of  $2\cdot 2k\Omega$  is advised.

#### PROGRAMMING/POWER UP

Data and signal input pins should not have input applied to them prior to the application of  $V_{DD}$ , as otherwise latch-up may occur.

## NJ8821

# FREQUENCY SYNTHESISER (MICROPROCESSOR INTERFACE) WITH RESETTABLE COUNTERS

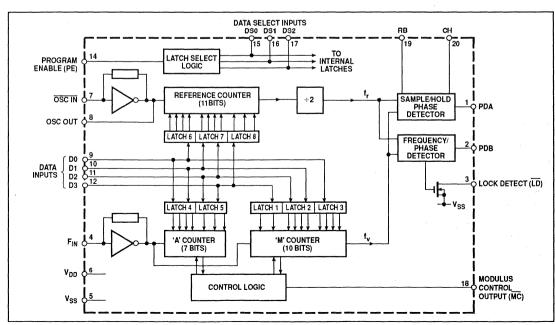

The NJ8821 is a synthesiser circuit fabricated on the GPS CMOS process and is capable of achieving high sideband attenuation and low noise performance. It contains a reference oscillator, 11-bit programmable reference divider, digital and sample-and-hold comparators, 10-bit programmable 'M' counter, 7-bit programmable 'A' counter and the necessary control and latch circuitry for accepting and latching the input data.

Data is presented as eight 4-bit words under external control from a suitable microprocessor.

It is intended to be used in conjunction with a two-modulus prescaler such as the SP8710 series to produce a universal binary coded synthesiser.

The NJ8821 is available in Plastic DIL (DP) and Miniature Plastic DIL (MP) packages, both with operating temperature range of -30°C to +70°C. The NJ8821MA is available only in Ceramic DIL package with operating temperature range of -40°C to +85°C.

#### **FEATURES**

- Low Power Consumption

- Microprocessor Compatible

- High Performance Sample and Hold Phase Detector

- >10MHz Input Frequency

#### ORDERING INFORMATION

NJ8821 BA DP Plastic DIL Package

NJ8821 BAMP Miniature Plastic DIL Package

NJ8821 MA DG Ceramic DIL Package

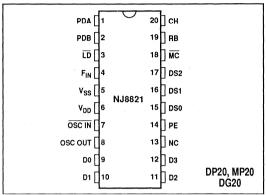

Fig.1 Pin connections - top view

#### ABSOLUTE MAXIMUM RATINGS

Supply voltage, V<sub>DD</sub>-V<sub>SS</sub>

Input voltage

Open drain output, pin 3

All other pins

Storage temperature

Storage temperature

7V V<sub>ss</sub>-0·3V to V<sub>DD</sub>+0·3V -65°C to +150°C (DG package, NJ8821MA) -55°C to +125°C

-0.5V to 7V

(DP and MP packages, NJ8821)

Fig.2 Block diagram

#### ELECTRICAL CHARACTERISTICS AT VDD = 5V

Test conditions unless otherwise stated:

$V_{DD}$ - $V_{SS}$ =5V ±0.5V. Temperature range NJ8821 BA: -30°C to +70°C; NJ8821MA: -40°C to +85°C DC Characteristics

| Characteristic               |                | Value |       | Units      | Conditions                                                 |

|------------------------------|----------------|-------|-------|------------|------------------------------------------------------------|

| Onaracter is to              | Min. Typ. Max. |       | Units | Conditions |                                                            |

| Supply current               |                | 3.5   | 5.5   | mA         | $f_{OSC}$ , $f_{FIN} = 10MHz \ 0 to 5V$                    |

|                              |                | 0.7   | 1.5   | mA         | f <sub>osc</sub> , f <sub>FIN</sub> = 1·0MHz } square wave |

| OUTPUT LEVELS                | l              | l     |       |            |                                                            |

| Modulus Control Output (MC)  | ١              |       |       |            |                                                            |

| High level                   | 4∙6            |       |       | V          | I <sub>SOURCE</sub> = 1mA                                  |

| Low level                    |                |       | 0.4   | V          | I <sub>SINK</sub> = 1mA                                    |

| Lock Detect Output (LD)      | 1              |       |       |            |                                                            |

| Low level                    |                |       | 0.4   | V          | I <sub>SINK</sub> = 4mA                                    |

| Open drain pull-up voltage   |                | ł     | 7     | ٧          |                                                            |

| PDB Output                   |                | 1     |       |            |                                                            |

| High level                   | 4∙6            | 1     |       | V          | I <sub>SOURCE</sub> = 5mA                                  |

| Low level                    |                | 1     | 0.4   | V          | I <sub>SINK</sub> = 5mA                                    |

| 3-state leakage current      | ļ              |       | ±0·1  | μΑ         |                                                            |

| INPUT LEVELS                 |                |       |       |            | ;                                                          |

| Data Inputs (D0-D3)          |                | l     |       |            |                                                            |

| High level                   | 4.25           | l     |       | V          | TTL compatible                                             |

| Low level                    |                | 1     | 0.4   | V          | See note 1                                                 |

| Program Enable Input (PE)    |                | 1     |       | 1          |                                                            |

| High level                   | 4.25           |       |       | V          |                                                            |

| Low level                    |                | l     | 0.75  | V          |                                                            |

| Data Select Inputs (DS0-DS2) | 1              |       |       |            |                                                            |

| High level                   | 4.25           |       |       | V          |                                                            |

| Low level                    |                |       | 0.75  | ٧          |                                                            |

#### **AC Characteristics**

| Characteristic                                                  |      | Value |      | Units | Conditions                                                           |  |

|-----------------------------------------------------------------|------|-------|------|-------|----------------------------------------------------------------------|--|

| Onal acteristic                                                 | Min. | Тур.  | Max. | Units |                                                                      |  |

| F <sub>IN</sub> and OSC IN input level                          | 200  |       |      | mVRMS | 10MHz AC-coupled sinewave                                            |  |

| Max. operating frequency, f <sub>FIN</sub> and f <sub>osc</sub> | 10.6 |       |      | MHz   | Input squarewave V <sub>DD</sub> to V <sub>SS</sub> ,<br>See note 4. |  |

| Propagation delay, clock to MC                                  |      | 30    | 50   | ns    | See note 2.                                                          |  |

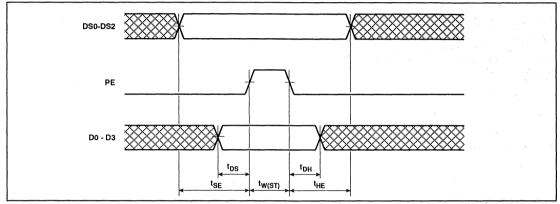

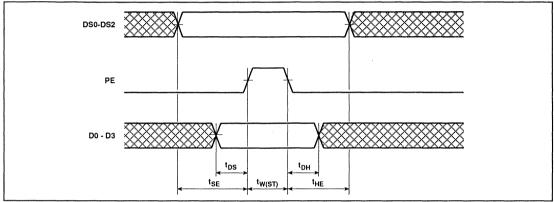

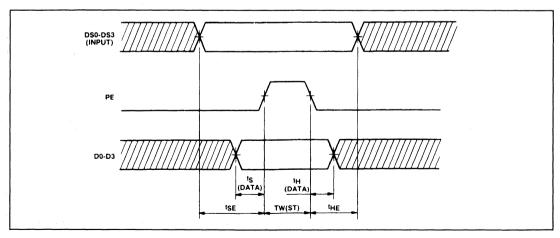

| Strobe pulse width, tw(ST)                                      | 2    |       |      | μs    | )                                                                    |  |

| Data set-up time, t <sub>DS</sub>                               | 1    |       | 1    | μs    |                                                                      |  |

| Data hold time, t <sub>DH</sub>                                 | 1    |       |      | μs    | See Fig. 6                                                           |  |

| Latch address set-up time, t <sub>SE</sub>                      | 1    | l     |      | μs    |                                                                      |  |

| Latch address hold time, tHE                                    | 1    |       | l    | μs    | J                                                                    |  |

| Digital phase detector propagation delay                        |      | 500   | 1    | ns    |                                                                      |  |

| Gain programming resistor, RB                                   | 5    |       | 1    | kΩ    | See note 3.                                                          |  |

| Hold capacitor, CH                                              |      |       | 1    | nF    |                                                                      |  |

| Output resistance, PDA                                          | -    | l     | 5    | kΩ    |                                                                      |  |

| Digital phase detector gain                                     |      | 0.4   |      | V/Rad |                                                                      |  |

#### NOTES

- 1. Data inputs have internal pull-up resistors to enable them to be driven from TTL outputs.

- 2. All counters have outputs directly synchronous with their respective clock rising edges.

3. The finite output resistance of the internal voltage follower and 'on' resistance of the sample switch driving this pin will add a finite time constant to the loop. An external 1nF hold capacitor will give a maximum time constant of 5μs, typically.

4. Operation at up to 15MHz is possible with a full logic swing but is not guaranteed.

#### **PIN DESCRIPTIONS**

| Pin no.      | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | PDA                | Analog output from the sample and hold phase comparator for use as a 'fine' error signal. Output at $(V_{DD}-V_{SS})/2$ when the system is in lock. Voltage increases as $f_V$ phase lead increases; voltage decreases as $f_V$ phase lead increases. Output is linear over only a narrow phase window, determined by gain (programmed by RB).                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2            | PDB                | Three-state output from the phase/frequency detector for use as a 'coarse' error signal. $f_V > f_\Gamma \text{ or } f_V \text{ leading: positive pulses with respect to the bias point } V_{\text{BIAS}} \\ f_V < f_\Gamma \text{ or } f_\Gamma \text{ leading: negative pulses with respect to the bias point } V_{\text{BIAS}} \\ f_V = f_\Gamma \text{ and phase error within PDA window: high impedance.}$                                                                                                                                                                                                                                                                                                                                                                                               |

| 3            | LD                 | An open-drain lock detect output at low level when phase error is within PDA window (in lock); high impedance at all other times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4            | F <sub>IN</sub>    | The input to the main counters, normally driven from a prescaler, which may be AC-coupled or, when a full logic swing is available, may be DC-coupled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5            | $V_{SS}$           | Negative supply (ground).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6            | $V_{DD}$           | Positive supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7, 8         | OSC IN/<br>OSC OUT | These pins form an on-chip reference oscillator when a series resonant crystal is connected across them. Capacitors of appropriate value are also required between each end of the crystal and ground to provide the necessary additional phase shift. An external reference signal may, alternatively, be applied to OSC IN. This may be a low-level signal, AC-coupled, or if a full logic swing is available it may be DC-coupled. The program range of the reference counter is 3 to 2047, with the division ratio being twice the programmed number.                                                                                                                                                                                                                                                     |

| 9,10, 11, 12 | D0-D3              | Data on these inputs is transferred to the internal data latches during the appropriate data read time slot. D3 is MSB, D0 is LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13           | NC                 | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14           | PE                 | This pin is used as a strobe for the data. A logic '1' on this pin transfers data from the D0-D3 pins to the internal latch addressed by the data select (DS0-DS2) pins . A logic '0' disables the data inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15, 16, 17   | DS0-DS2            | Data select inputs for addressing the internal data latches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18           | MC                 | Modulus control output for controlling an external dual-modulus prescaler. $\overline{MC}$ will be low at the beginning of a count cycle and will remain low until the 'A' counter completes its cycle. $\overline{MC}$ then goes high and remains high until the 'M' counter completes its cycle, at which point both 'A' and 'M' counters are reset. This gives a total division ratio of $MP+A$ , where $P$ and $P+1$ represent the dual-modulus prescaler values. The program range of the 'A' counter is 0-127 and therefore can control prescalers with a division ratio up to and including $\div 128/129$ . The programming range of the 'M' counter is 8-1023 and, for correct operation, $M \ge A$ . Where every possible channel is required, the minimum total division ratio should be $P^2-P$ . |

| 19           | RB                 | An external sample and hold phase comparator gain programming resistor should be connected between this pin and $\rm V_{\rm SS}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20           | СН                 | An external hold capacitor should be connected between this pin and $V_{SS}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

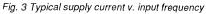

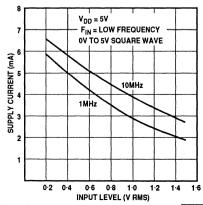

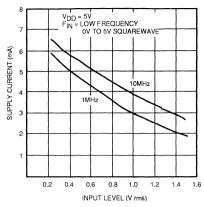

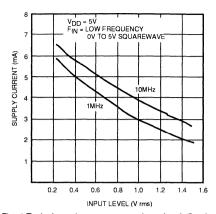

Fig. 4 Typical supply current v. input level, OSC IN

#### **PROGRAMMING**

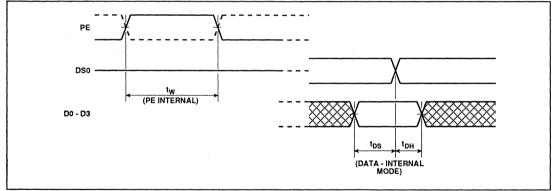

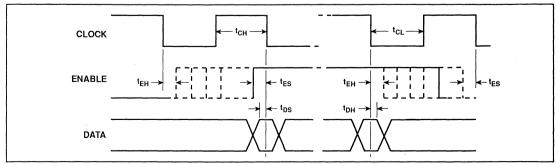

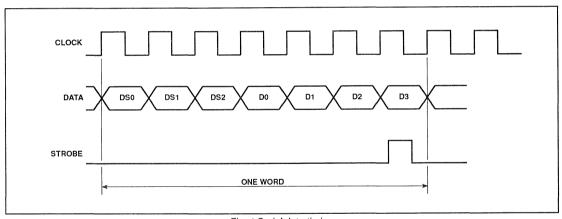

Timing is generated externally, normally from a microprocessor, and allows the user to change the data in selected latches as defined by the data map Fig.5. The PE pin is used as a strobe for the data: taking PE high causes data to be transferred from the data pins (D0-D3) into the addressed latch. Following the falling edge of PE, the data is retained in the addressed latch and the data inputs are disabled. Data transfer from all internal latches into the counters occurs simultaneously with the transfer of data into latch 1, which would therefore normally be the last latch addressed during each channel change. Timing information for this mode of operation is given in Fig. 6.

When re-programming, a reset to zero state is followed by reloading with the new counter values. This means that the synthesiser loop lock-up time is well defined and less than

10ms. If shorter lock-up times are are required when making only small changes in frequency, the GPS NJ8823 (with non-resettable counters) should be considered.

| WORD                                 | DS2                             | DS1                        | DS0                             | D3                                    | D2                                            | D1                                     | D0                                     |

|--------------------------------------|---------------------------------|----------------------------|---------------------------------|---------------------------------------|-----------------------------------------------|----------------------------------------|----------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | M1<br>M5<br>M9<br>A3<br>-<br>R3<br>R7 | M0<br>M4<br>M8<br>A2<br>A6<br>R2<br>R6<br>R10 | M3<br>M7<br>A1<br>A5<br>R1<br>R5<br>R9 | M2<br>M6<br>A0<br>A4<br>R0<br>R4<br>R8 |

Fig. 5 Data map

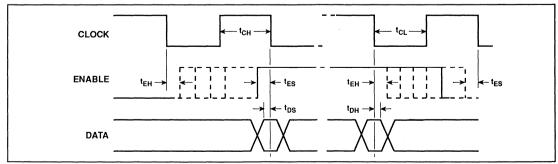

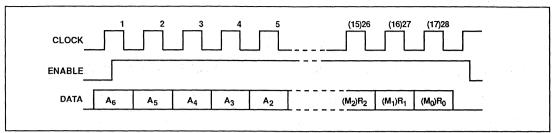

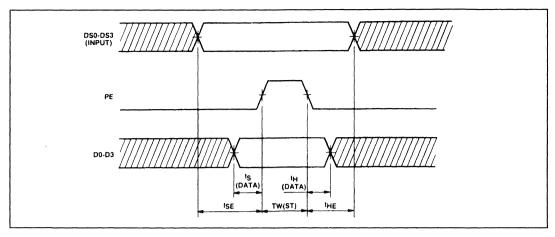

Fig. 6 Timing diagram

#### PHASE COMPARATORS

The digital phase/frequency detector drives a three-state output, PDB, which provides a 'coarse' error signal to enable fast switching between channels. The PDB output is active until the phase error is within the sample and hold phase detector, PDA, window, when PDB becomes high impedance. Phase-lock is indicated at this point by a low level on LD. The sample and hold phase detector provides a 'fine' error signal to give further phase adjustment and to hold the loop in lock.

An internally generated ramp, controlled by the digital output from both the reference and main divider chains, is sampled at the reference frequency to give the 'fine' error signal, PDA. When in phase lock, this output would be typically at  $(V_{DD}-V_{SS})/2$  and any offset from this would be proportional to phase error. The relationship between this offset and the

phase error is the phase comparator gain, which is programmable with an external resistor, RB. An internal 50pF capacitor is used in the sample and hold comparator.

#### **CRYSTAL OSCILLATOR**

When using the internal oscillator, the stability may be enhanced at high frequencies by the inclusion of a resistor between pin 8 (OSC OUT) and the other components. A value of  $150-270\Omega$  is advised.

#### PROGRAMMING/POWER UP

Data and signal input pins should not have input applied to them prior to the application of  $V_{DD}$ , as otherwise latch-up may occur.

# NJ88C22

# FREQUENCY SYNTHESISER (MICROPROCESSOR SERIAL INTERFACE) WITH RESETTABLE COUNTERS

The NJ88C22 is a synthesiser circuit fabricated on the GPS CMOS process and is capable of achieving high sideband attenuation and low noise performance. It contains a reference oscillator, 11-bit programmable reference divider, digital and sample-and-hold comparators, 10-bit programmable 'M' counter, 7-bit programmable 'A' counter and the necessary control and latch circuitry for accepting and latching the input data.

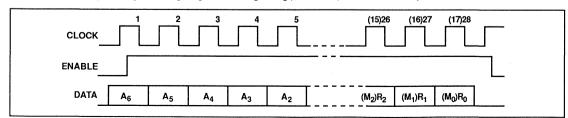

Data is presented serially under external control from a suitable microprocessor. Although 28 bits of data are initially required to program all counters, subsequent updating can be abbreviated to 17 bits, when only the 'A' and 'M' counters require changing.

The NJ88C22 is intended to be used in conjunction with a two-modulus prescaler such as the SP8710 or SP8705 series to produce a universal binary coded synthesiser for up to 1100MHz operation.

#### **FEATURES**

- Low Power Consumption

- High Performance Sample and Hold Phase Detector

- Serial Input with Fast Update Feature

- >20MHz Input Frequency

- Fast Lock-up Time

#### ORDERING INFORMATION

NJ88C22 MA DG Ceramic DIL Package NJ88C22 MA DP Plastic DIL Package

NJ88C22 MA MP Miniature Plastic DIL Package

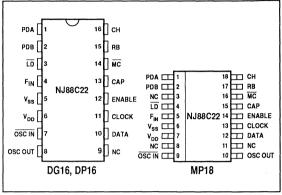

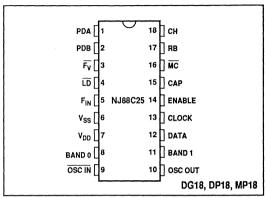

Fig.1 Pin connections - top view (not to scale)

#### **ABSOLUTE MAXIMUM RATINGS**

Supply voltage,  $V_{DD}-V_{SS}$ : -0.75 V to 7 V Input voltage Open drain output,  $\overline{LD}$  pin: All other pins:  $V_{SS}-0.3 V$  to  $V_{DD}+0.3 V$  Storage temperature:  $-55 ^{\circ} C$  to  $+125 ^{\circ} C$  (DP and MP packages)  $-65 ^{\circ} C$  to  $+150 ^{\circ} C$  (DG package)

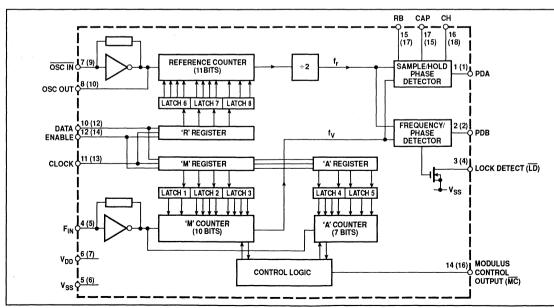

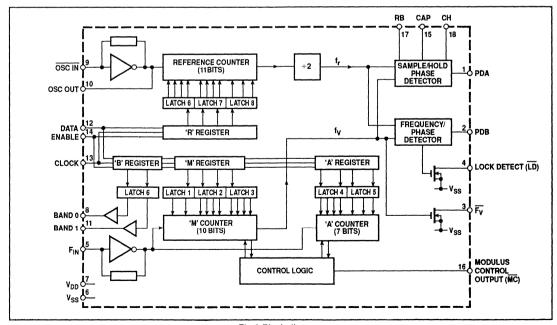

Fig.2 Block diagram (MP pinout shown in parentheses)

#### ELECTRICAL CHARACTERISTICS AT VDD = 5V

Test conditions unless otherwise stated:

$V_{DD}-V_{SS}=5V \pm 0.5V$ . Temperature range = -40°C to +85°C

#### DC Characteristics

| Characteristic              | Value |  |            | Units    | Conditions                                        |

|-----------------------------|-------|--|------------|----------|---------------------------------------------------|

| Characteristic              | Min.  |  | Max.       | Units    | Conditions                                        |

| Supply current              |       |  | 5·5<br>1.5 | mA<br>mA | $f_{OSC}$ , $f_{FIN} = 10MHz$ 0 to 5V square wave |

| Modulus Control Output (MC) |       |  |            |          | y wave                                            |

| High level                  | 4.6   |  | - 1        | V        | I <sub>SOURCE</sub> = 1 mA                        |

| Low level                   |       |  | 0.4        | l v      | I <sub>SINK</sub> = 1mA                           |

| Lock Detect Output (LD)     |       |  |            |          |                                                   |

| Low level                   |       |  | 0.4        | V        | I <sub>SINK</sub> = 4mA                           |

| Open drain pull-up voltage  |       |  | 7.0        | V        |                                                   |

| PDB Output                  | 1     |  |            |          |                                                   |

| High level                  | 4.6   |  |            | V        | I <sub>SOURCE</sub> = 5mA                         |

| Low level                   |       |  | 0.4        | V        | I <sub>SINK</sub> = 5mA                           |

| 3-state leakage current     |       |  | ±0·1       | μА       |                                                   |

#### **AC Characteristics**

| Characteristic                                                  |      | Value |                      |        | Conditions                                                     |  |

|-----------------------------------------------------------------|------|-------|----------------------|--------|----------------------------------------------------------------|--|

| Characteristic                                                  | Min. | Тур.  | Max.                 | Units  | Conditions                                                     |  |

| F <sub>IN</sub> and OSC IN input level                          | 200  |       |                      | mV RMS | ·                                                              |  |

| Max. operating frequency, f <sub>FIN</sub> and f <sub>osc</sub> | 20   |       |                      | MHz    | Input squarewave V <sub>DD</sub> to V <sub>SS</sub> ,<br>25°C. |  |

| Propagation delay, clock to modulus control MC                  |      | 30    | 50                   | ns     | See note 2                                                     |  |

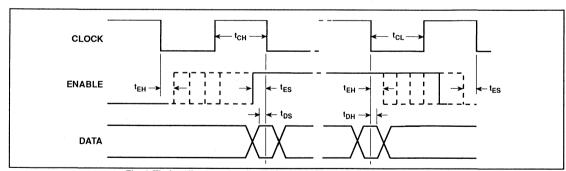

| Programming Inputs                                              |      |       |                      |        |                                                                |  |

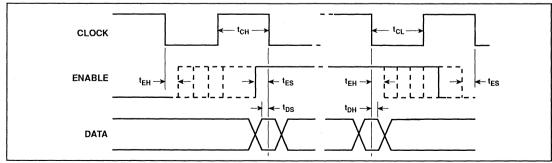

| Clock high time, t <sub>CH</sub>                                | 0.5  |       |                      | μs     | )                                                              |  |

| Clock low time, t <sub>CL</sub>                                 | 0.5  |       |                      | μs     | All timing periods                                             |  |

| Enable set-up time, t <sub>ES</sub>                             | 0.2  |       | t <sub>CH</sub>      | μs     | are referenced to                                              |  |

| Enable hold time, t <sub>EH</sub>                               | 0.2  |       |                      | μs     | the negative                                                   |  |

| Data set-up time, t <sub>DS</sub>                               | 0.2  |       |                      | μs     | transition of the                                              |  |

| Data hold time, t <sub>DH</sub>                                 | 0.2  |       |                      | μs     | clock waveform                                                 |  |

| Clock rise and fall times                                       |      | 1     | 0.2                  | μs     | J                                                              |  |

| High level threshold                                            |      |       | V <sub>DD</sub> −0·8 | · V    | See note 1                                                     |  |

| Low level threshold                                             | 0.8  |       |                      | V      | See note 1                                                     |  |

| Hysteresis                                                      | 1.0  |       |                      | V      | See note 1                                                     |  |

| Phase Detector                                                  |      |       |                      |        |                                                                |  |

| Digital phase detector propagation delay                        |      | 500   |                      | ns     |                                                                |  |

| Gain programming resistor, RB                                   | 5    |       |                      | kΩ     |                                                                |  |

| Hold capacitor, CH                                              |      |       | 1                    | nF     | See note 3                                                     |  |

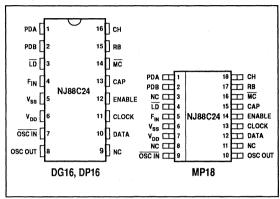

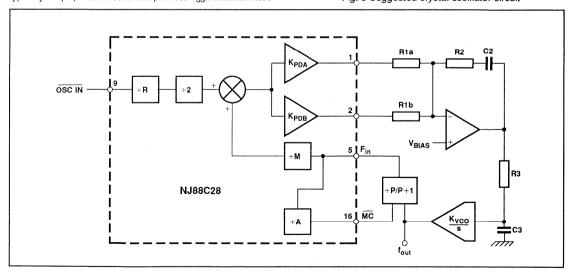

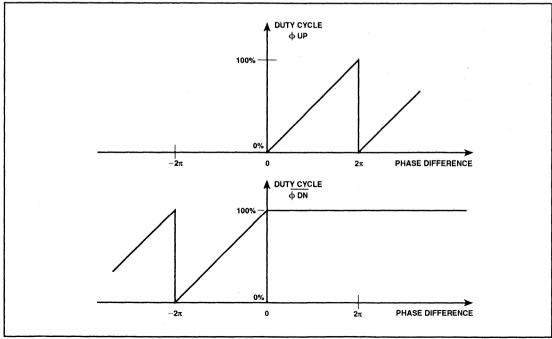

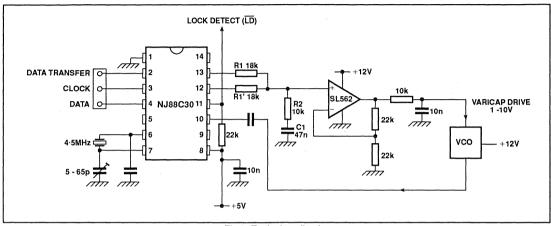

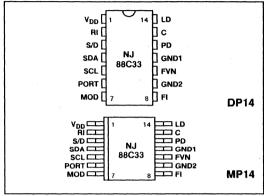

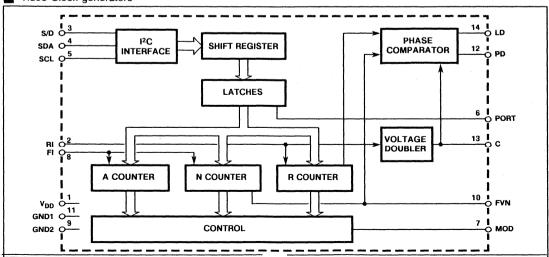

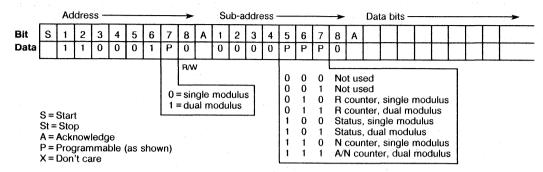

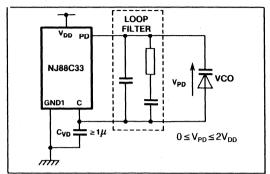

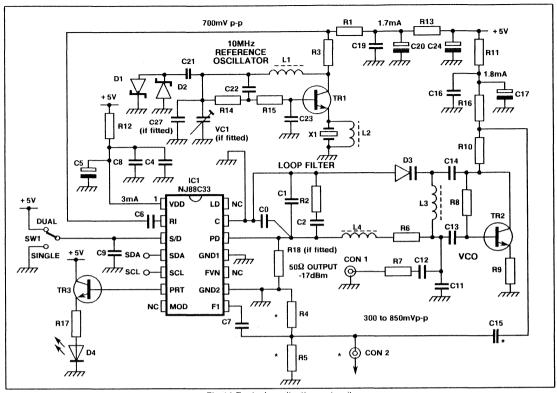

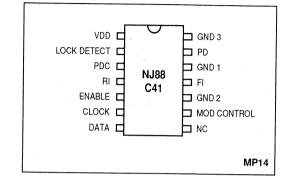

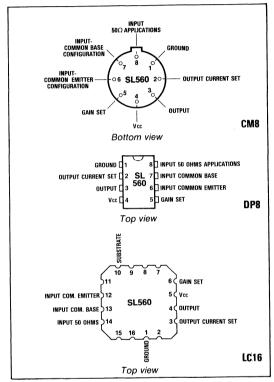

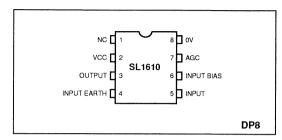

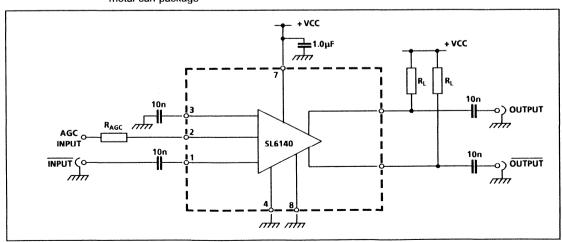

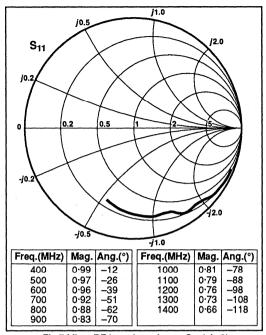

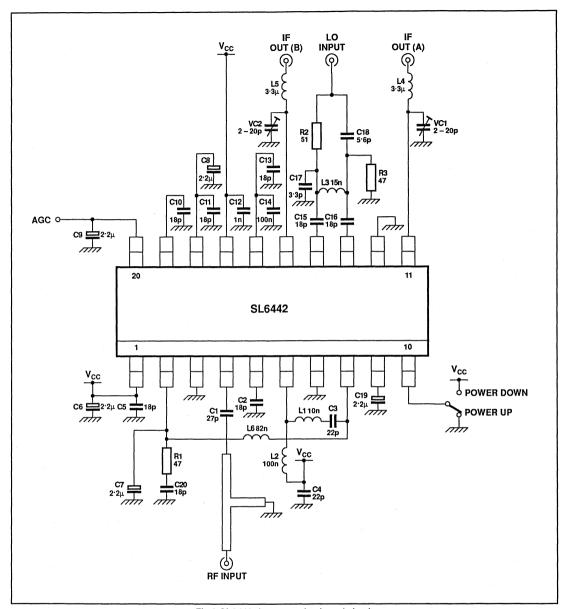

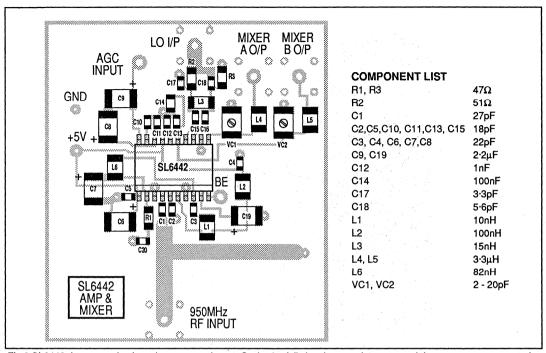

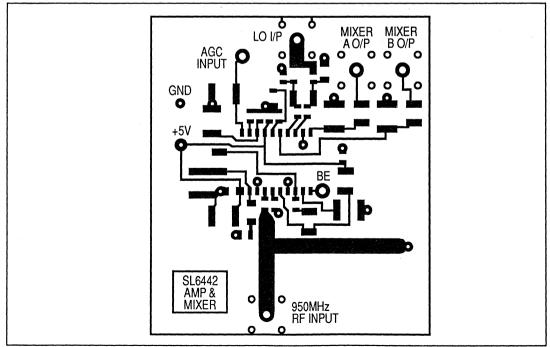

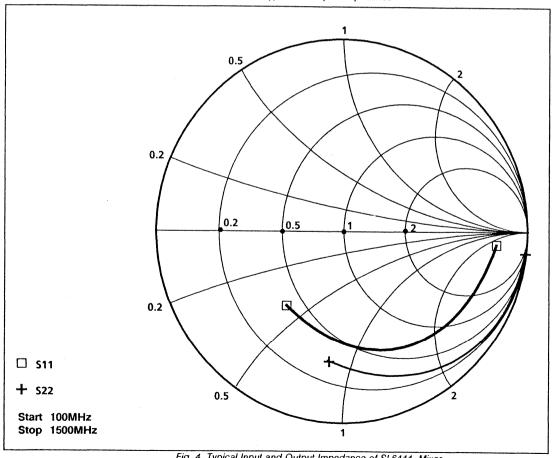

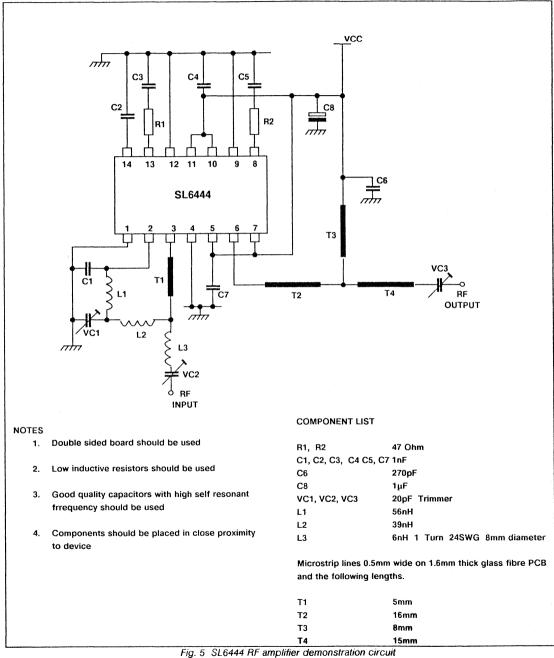

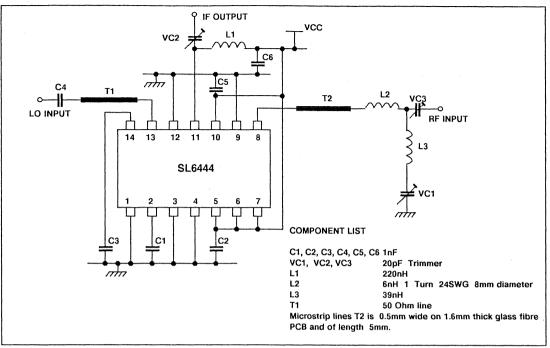

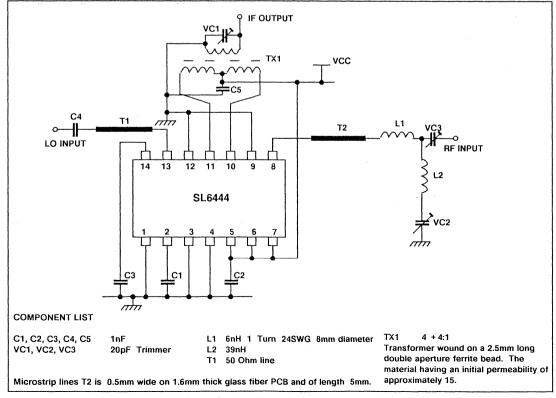

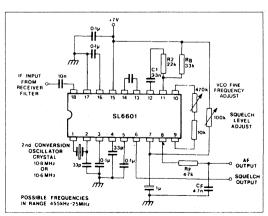

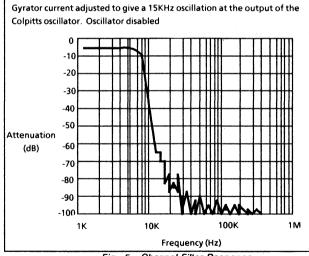

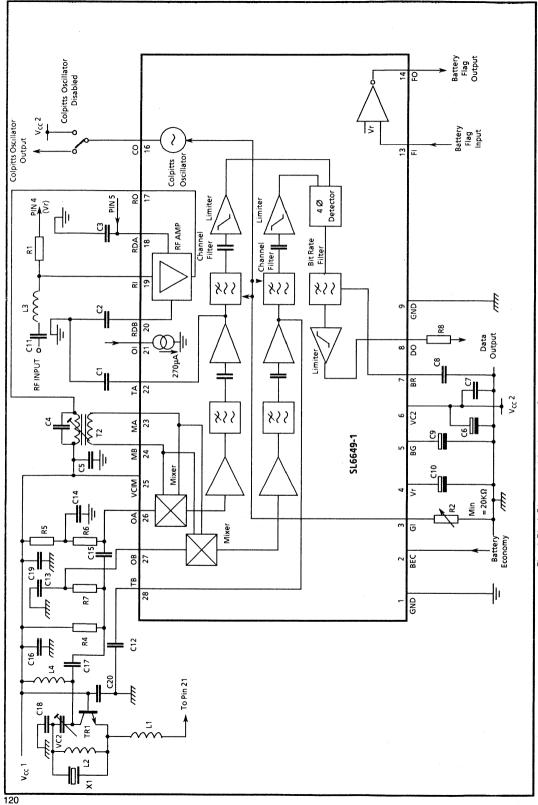

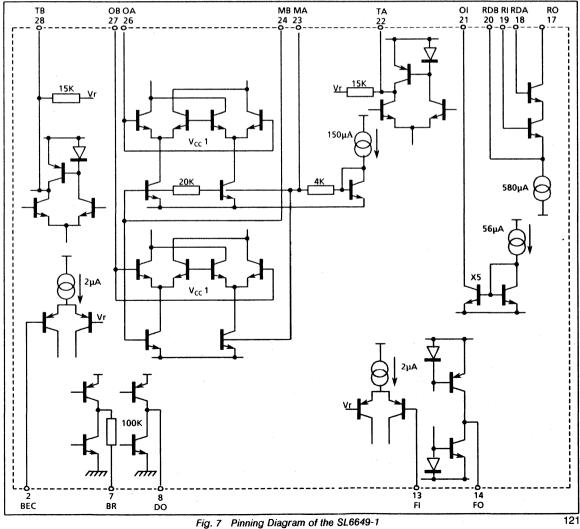

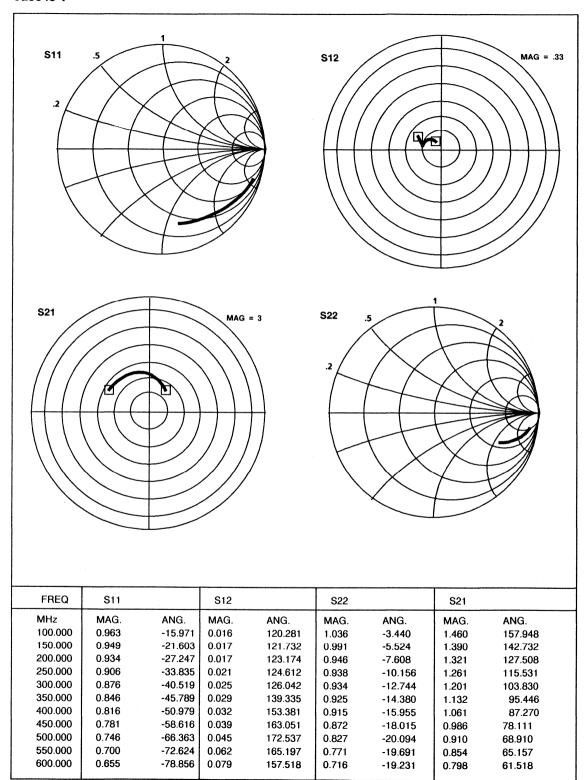

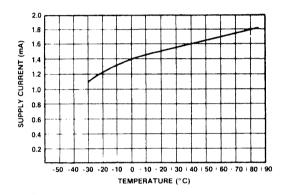

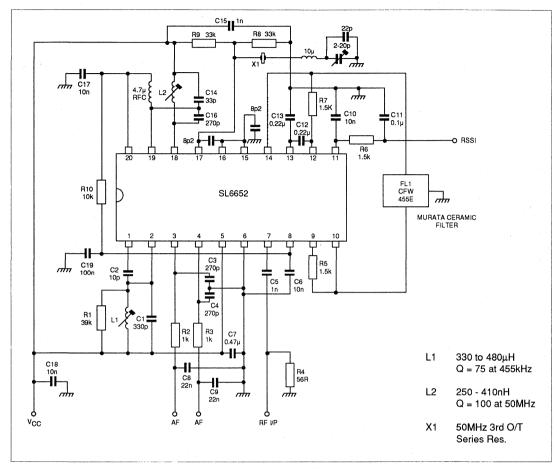

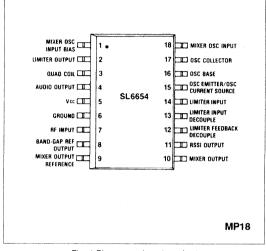

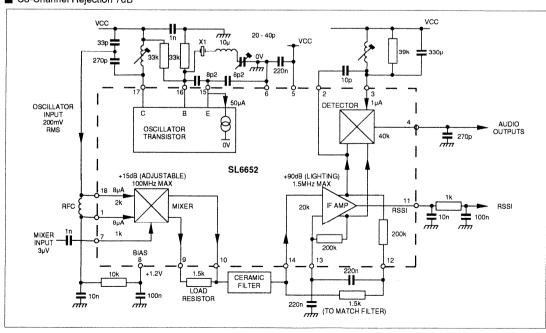

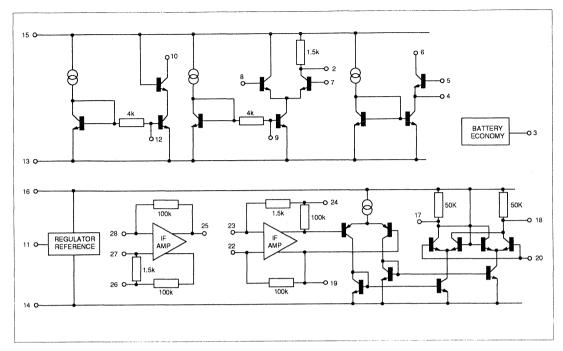

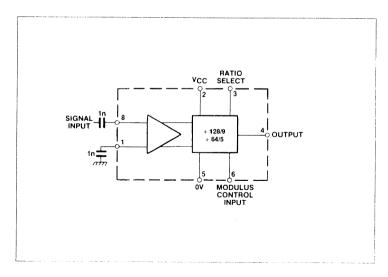

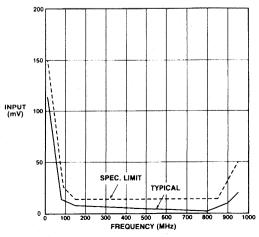

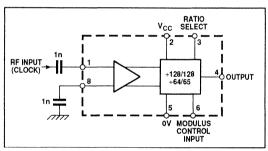

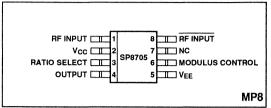

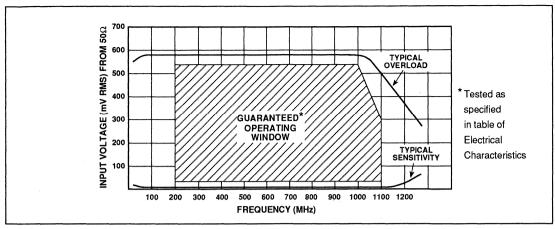

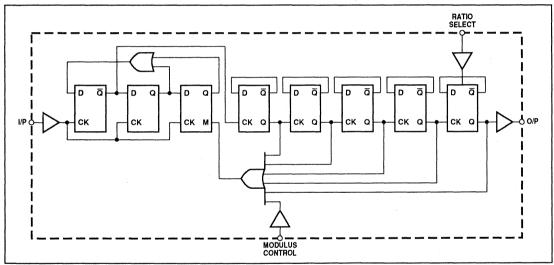

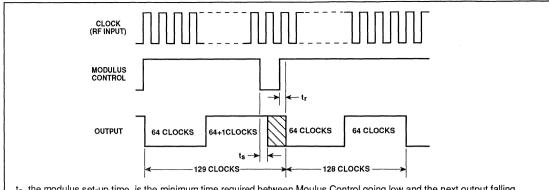

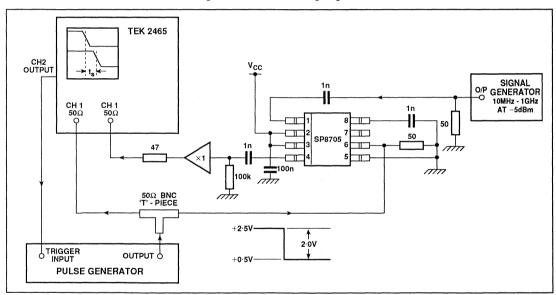

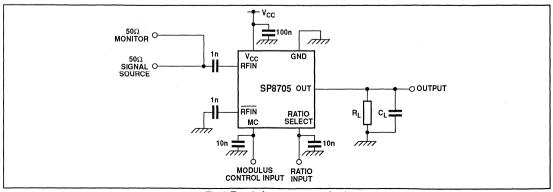

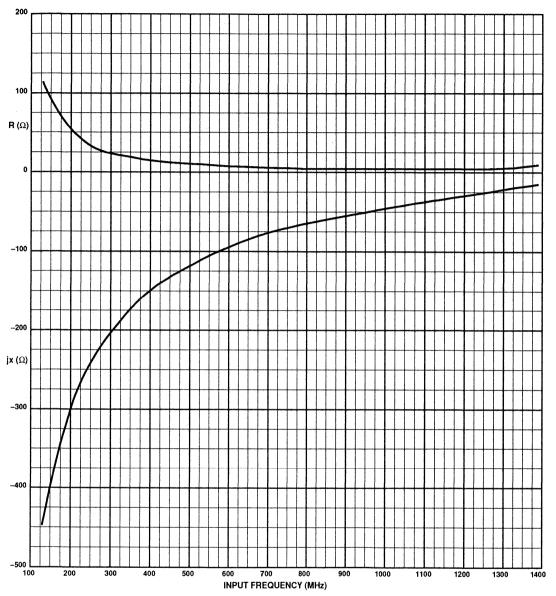

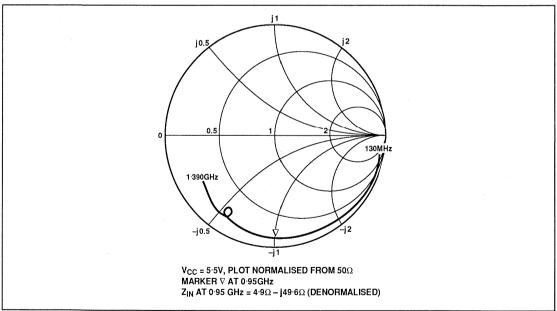

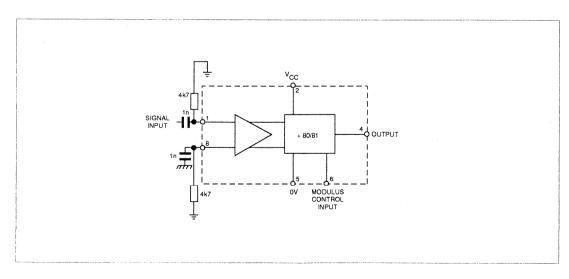

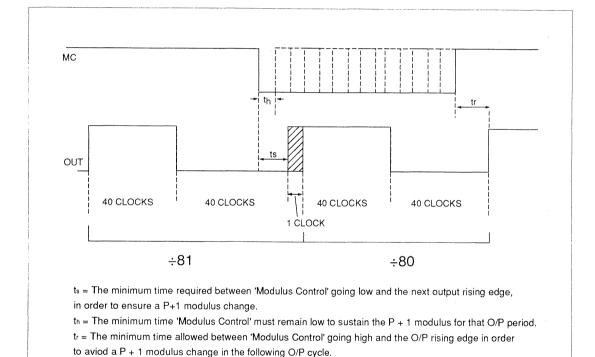

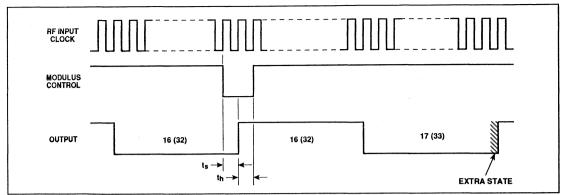

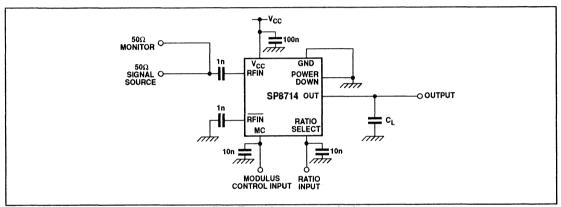

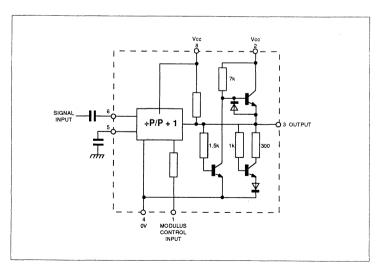

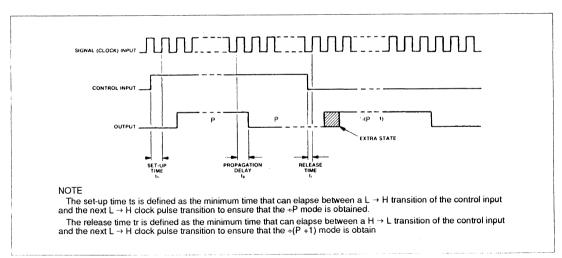

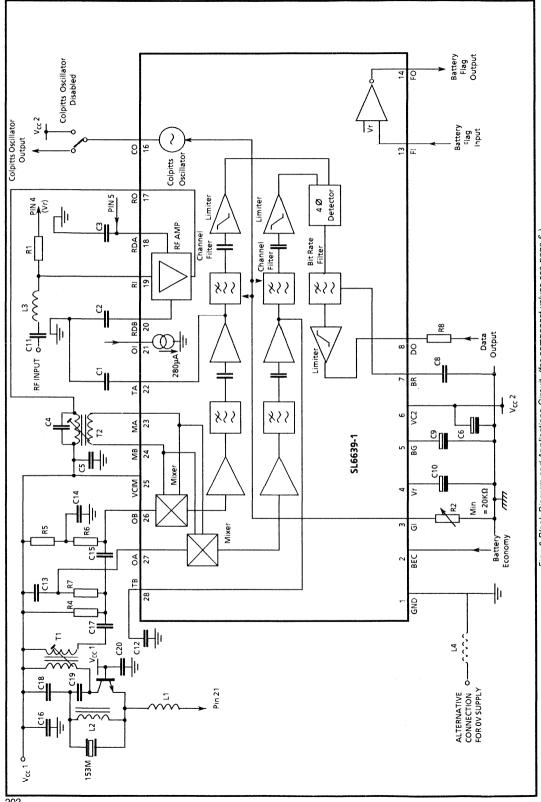

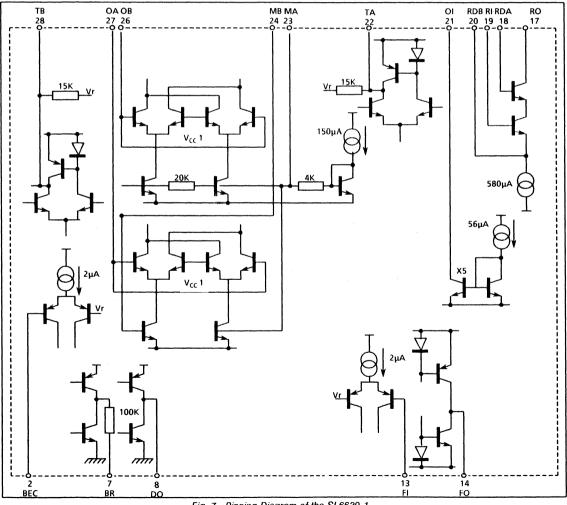

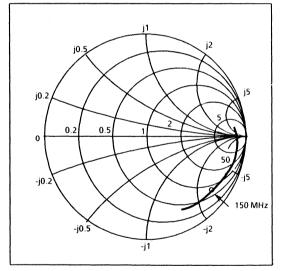

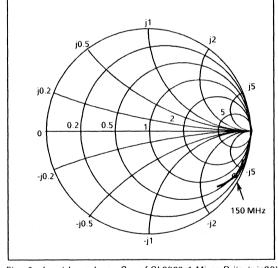

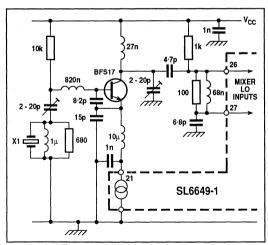

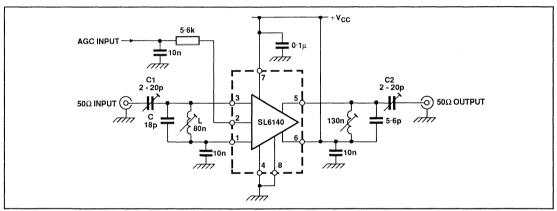

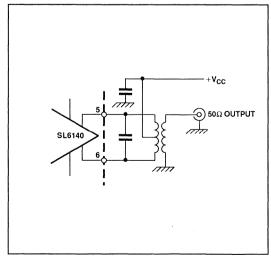

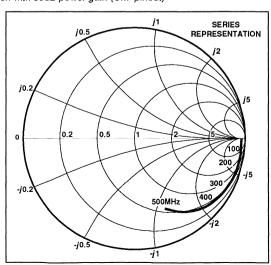

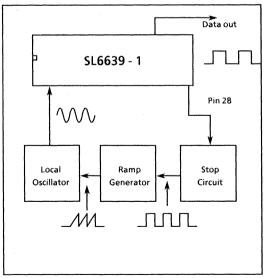

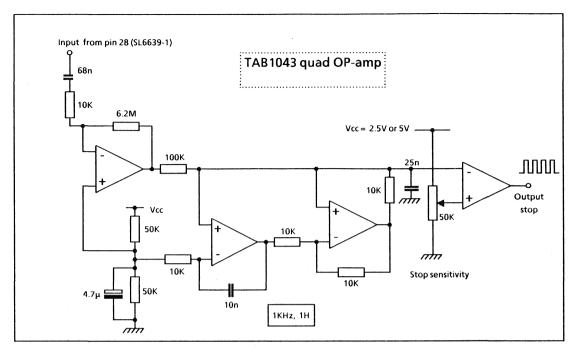

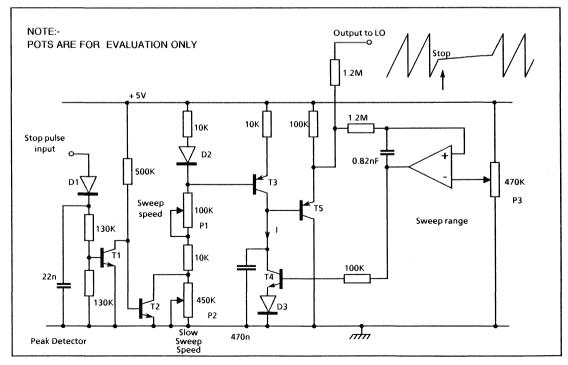

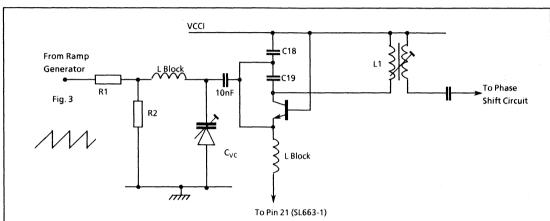

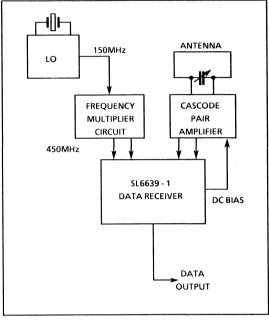

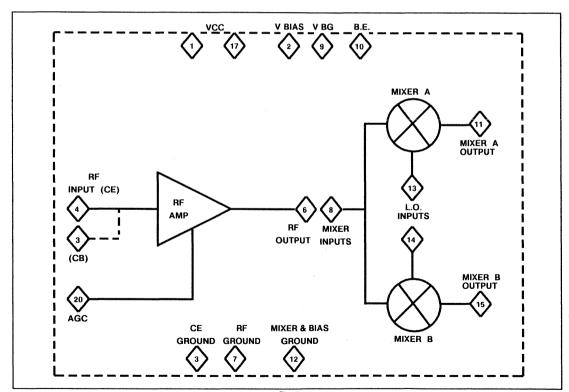

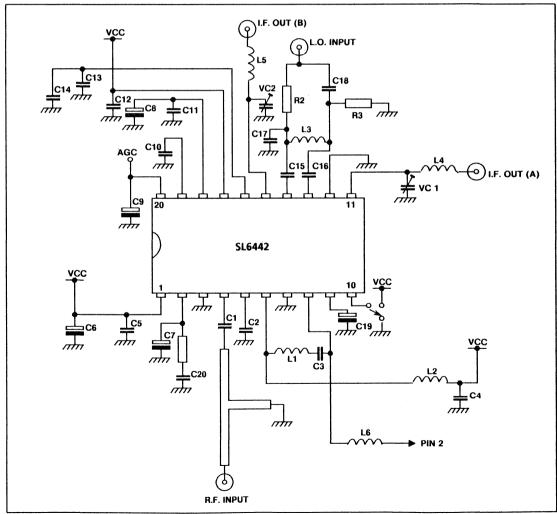

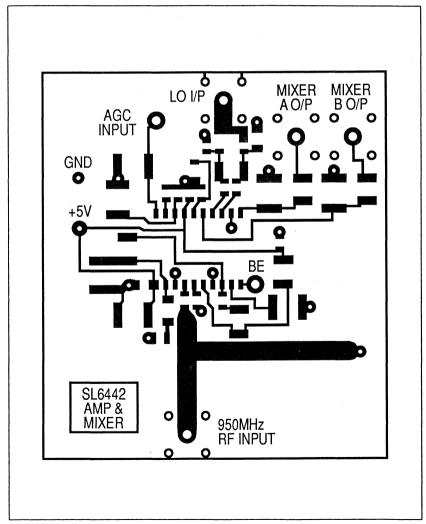

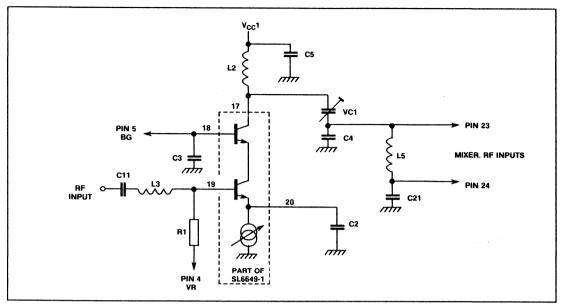

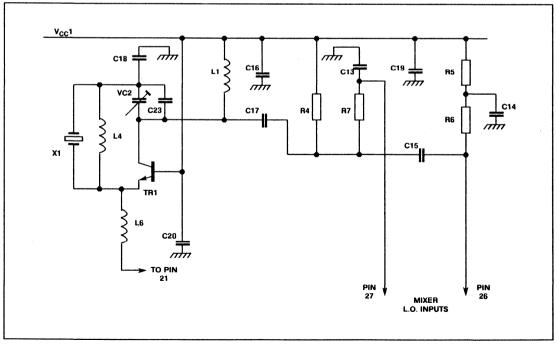

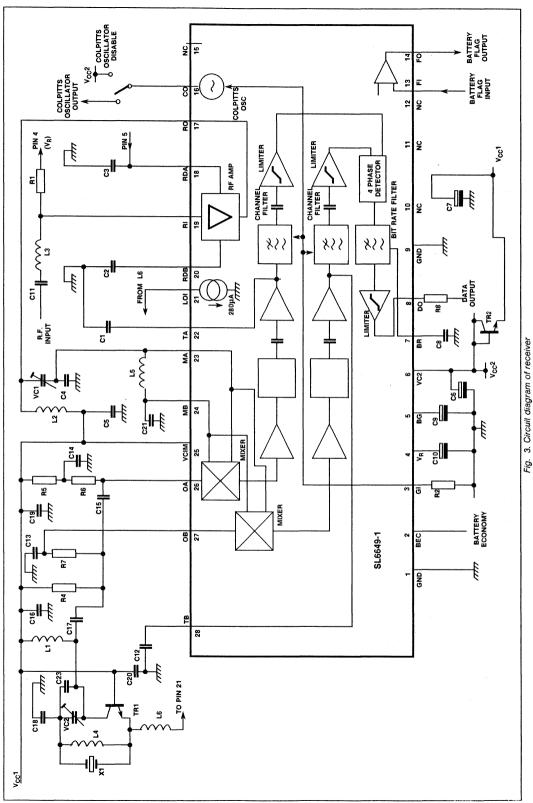

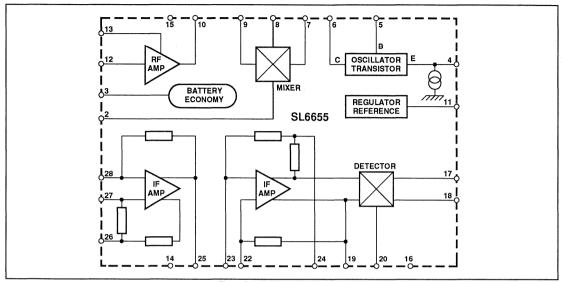

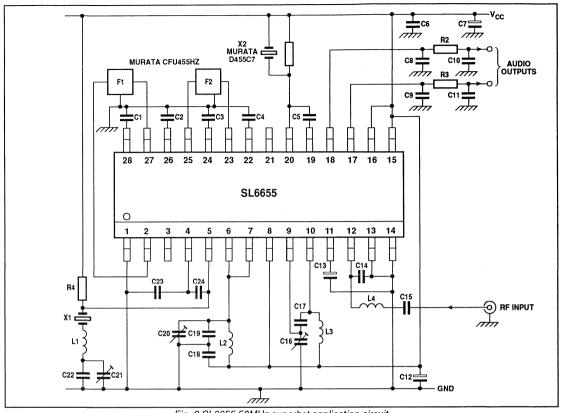

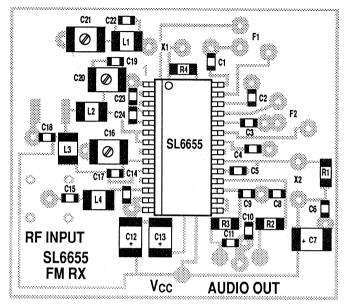

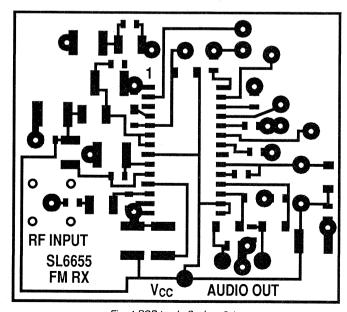

| Programming capacitor, CAP                                      |      |       | 1                    | nF     |                                                                |  |